# TMS320C55x DSP Programmer's Guide

## **Preliminary Draft**

This document contains preliminary data current as of the publication date and is subject to change without notice.

SPRU376 April 2000

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated

#### **Preface**

### **Read This First**

#### About This Manual

This manual describes ways to optimize C and assembly code for the TMS320C55x<sup>TM</sup> DSPs and recommends ways to write TMS320C55x code for specific applications.

#### **Notational Conventions**

This document uses the following conventions.

- The device number TMS320C55x is often abbreviated as C55x.

- ☐ Program listings, program examples, and interactive displays are shown in a special typeface similar to a typewriter's. Examples use a bold version of the special typeface for emphasis; interactive displays use a bold version of the special typeface to distinguish commands that you enter from items that the system displays (such as prompts, command output, error messages, etc.).

Here is a sample program listing:

```

0011

0005

0001

.field

1, 2

0012

0005

0003

.field

3, 4

0013

0005

0006

.field

6, 3

0014

0006

.even

```

Here is an example of a system prompt and a command that you might enter:

```

C: csr -a /user/ti/simuboard/utilities

```

☐ In syntax descriptions, the instruction, command, or directive is in a **bold typeface** font and parameters are in an *italic typeface*. Portions of a syntax that are in **bold** should be entered as shown; portions of a syntax that are in *italics* describe the type of information that should be entered. Here is an example of a directive syntax:

```

.asect "section name", address

```

.asect is the directive. This directive has two parameters, indicated by *section name* and *address*. When you use .asect, the first parameter must be an actual section name, enclosed in double quotes; the second parameter must be an address.

| Some directives can have a varying number of parameters. For example,      |

|----------------------------------------------------------------------------|

| the .byte directive can have up to 100 parameters. The syntax for this di- |

| rective is:                                                                |

This syntax shows that .byte must have at least one value parameter, but you have the option of supplying additional value parameters, separated by commas.

☐ In most cases, hexadecimal numbers are shown with the suffix h. For example, the following number is a hexadecimal 40 (decimal 64):

40h

Similarly, binary numbers usually are shown with the suffix b. For example, the following number is the decimal number 4 shown in binary form:

0100b

☐ Bits are sometimes referenced with the following notation:

| Notation      | Description                  | Example                                                                 |

|---------------|------------------------------|-------------------------------------------------------------------------|

| Register(n-m) | Bits n through m of Register | AC0(15–0) represents the 16 least significant bits of the register AC0. |

#### Related Documentation From Texas Instruments

The following books describe the TMS320C55x devices and related support tools. To obtain a copy of any of these TI documents, call the Texas Instruments Literature Response Center at (800) 477-8924. When ordering, please identify the book by its title and literature number.

- TMS320C55x Technical Overview (SPRU393). This overview is an introduction to the TMS320C55x digital signal processor (DSP). The TMS320C55x is the latest generation of fixed-point DSPs in the TMS320C5000 DSP platform. Like the previous generations, this processor is optimized for high performance and low-power operation. This book describes the CPU architecture, low-power enhancements, and embedded emulation features of the TMS320C55x.

- **TMS320C55x DSP CPU Reference Guide** (literature number SPRU371) describes the architecture, registers, and operation of the CPU. This book also describes how to make individual portions of the DSP inactive to save power.

- **TMS320C55x DSP Mnemonic Instruction Set Reference Guide** (literature number SPRU374) describes the mnemonic instructions individually. It also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the algebraic instruction set.

- **TMS320C55x DSP Algebraic Instruction Set Reference Guide** (literature number SPRU375) describes the algebraic instructions individually. It also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the mnemonic instruction set.

- TMS320C55x Optimizing C Compiler User's Guide (literature number SPRU281) describes the 'C55x C compiler. This C compiler accepts ANSI standard C source code and produces assembly language source code for TMS320C55x devices.

- **TMS320C55x Assembly Language Tools User's Guide** (literature number SPRU280) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for TMS320C55x devices.

The CPU, the registers, and the instruction sets are also described in online documentation contained in Code Composer Studio™.

#### Trademarks

Code Composer Studio, TMS320C54x, C54x, TMS320C55x, and C55x are trademarks of Texas Instruments.

## **Contents**

| 1 | Intro | oduction                                                                               | 1-1           |

|---|-------|----------------------------------------------------------------------------------------|---------------|

|   |       | s some key features of the TMS320C55x DSP architecture and recommends are development. | a process for |

|   | 1.1   | TMS320C55x Architecture                                                                | 1-2           |

|   | 1.2   | Code Development Flow for Best Performance                                             | 1-3           |

| 2 | Tutor | rial                                                                                   | 2-1           |

|   | Uses  | s example code to walk you through the code development flow for the TMS32             | 20C55x DSP.   |

|   | 2.1   | Introduction                                                                           | 2-2           |

|   | 2.2   | Writing Assembly Code                                                                  | 2-3           |

|   |       | 2.2.1 Allocate Sections for Code, Constants, and Variables                             | 2-5           |

|   |       | 2.2.2 Processor Mode Initialization                                                    | 2-7           |

|   |       | 2.2.3 Setting up Addressing Modes                                                      | 2-8           |

|   | 2.3   | Understanding the Linking Process                                                      | 2-10          |

|   | 2.4   | Building Your Program                                                                  | 2-14          |

|   |       | 2.4.1 Creating a Project                                                               |               |

|   |       | 2.4.2 Adding Files to the Work space                                                   |               |

|   |       | 2.4.3 Modifying Build Options                                                          |               |

|   |       | 2.4.4 Build the Program                                                                |               |

|   | 2.5   | Testing your code                                                                      |               |

|   | 2.6   | Benchmarking your code                                                                 | 2-18          |

| 3 | Optin | mizing C Code                                                                          | 3-1           |

|   |       | cribes how to optimize your C code using compiler options, intrinsics sformations.     | s, and code   |

|   | 3.1   | The Compiler and Its Options                                                           | 3-2           |

|   | 3.2   | Using Program-level Optimization                                                       |               |

|   | 3.3   | Using Function Inlining                                                                | 3-10          |

|   |       | 3.3.1 Using –oi <size> option</size>                                                   | 3-10          |

|   | 3.4   | Using Intrinsics                                                                       | 3-12          |

|   | 3.5   | Using Long Data Accesses for 16-Bit Data                                               | 3-16          |

|   | 3.6   | Genera   | ating Efficient Loop Code                                                | 3-17 |

|---|-------|----------|--------------------------------------------------------------------------|------|

|   |       | 3.6.1    | Avoid function calls in repeated loops                                   | 3-17 |

|   |       | 3.6.2    | Keep loops small to enable local repeat                                  | 3-17 |

|   |       | 3.6.3    | Trip Count Issues                                                        | 3-18 |

|   |       | 3.6.4    | Using Unsigned Integer Types for Trip Counter                            | 3-19 |

|   |       | 3.6.5    | Use _nassert Intrinsic                                                   | 3-21 |

|   |       | 3.6.6    | Use -o3 and -pm Compiler Options                                         | 3-24 |

|   | 3.7   | Genera   | ating Efficient Control Code                                             | 3-27 |

|   | 3.8   | Efficier | nt Math Operations                                                       | 3-28 |

|   |       | 3.8.1    | Use 16-bit Data Types Whenever Possible                                  | 3-28 |

|   |       | 3.8.2    | Special Considerations When Using MAC Constructs                         | 3-28 |

|   |       | 3.8.3    | Avoid Using Modulus Operator When Simulating                             |      |

|   |       |          | Circular Addressing in C                                                 |      |

|   | 3.9   |          | ry Management                                                            |      |

|   |       | 3.9.1    | Avoiding Holes Caused by Data Alignment                                  |      |

|   |       | 3.9.2    | Local vs Global Symbol Declarations                                      |      |

|   |       | 3.9.3    | Stack Configuration                                                      |      |

|   |       | 3.9.4    | Allocating Code and Data in the TMS320C55x Memory Map                    |      |

|   | 3.10  | Allocat  | ting Function Code to Different Sections                                 | 3-40 |

| 4 | Optin | nizina A | Assembly Code                                                            | 4-1  |

|   | •     | _        | me of the opportunities for optimizing TMS320C55x assembly code and prov |      |

|   |       |          | g code examples.                                                         |      |

|   | 4.1   | -        | nt Use of the Dual-MAC Hardware                                          | 1-2  |

|   | 4.1   | 4.1.1    | Data Memory Pointer Usage                                                |      |

|   |       | 4.1.2    | Multi-Channel Applications                                               |      |

|   |       | 4.1.3    | Multi-Algorithm Applications                                             |      |

|   |       | 4.1.4    | Implicit Algorithm Symmetry                                              |      |

|   |       | 4.1.5    | Loop Unrolling                                                           |      |

|   | 4.2   |          | Parallel Execution Features                                              |      |

|   | 1.2   | 4.2.1    | Built-In Parallelism                                                     |      |

|   |       | 4.2.2    | User-Defined Parallelism                                                 |      |

|   |       | 4.2.3    | Architectural Features Supporting Parallelism                            |      |

|   |       | 4.2.4    | User-Defined Parallelism Rules                                           |      |

|   |       | 4.2.5    | Process for Implementing User-Defined Parallelism                        |      |

|   |       | 4.2.6    | Parallelism Tips                                                         |      |

|   |       | 4.2.7    | Examples of Parallel Optimization Within CPU Functional Units            |      |

|   |       | 4.2.8    | Example of Parallel Optimization Across the A-Unit, P-Unit, and D-Unit   |      |

|   | 4.3   |          | nenting Efficient Loops                                                  |      |

|   |       | 4.3.1    | Nesting of Loops                                                         |      |

|   |       | 4.3.2    | Efficient Use of repeat(CSR) Looping                                     |      |

|   |       | 4.3.3    | Avoiding Pipeline Delays When Accessing Loop-Control Registers           |      |

|   | 4.4   |          | zing Instruction Pipeline Delays                                         |      |

|   | -     | 4.4.1    | Process to Resolve Pipeline Conflicts                                    |      |

|   |       | 4.4.2    | Recommendations for Preventing Pipeline Delays                           |      |

|   |       | 113      | ŭ ,                                                                      |      |

| 5 | Fixed  | J-Point Arithmetic                                                                                             |

|---|--------|----------------------------------------------------------------------------------------------------------------|

|   |        | nins important considerations for doing fixed-point arithmetic with the TMS320C55x DSP. des code examples.     |

|   | 5.1    | Fixed-Point Arithmetic 5-2                                                                                     |

|   |        | 5.1.1 2s-Complement Numbers 5-2                                                                                |

|   |        | 5.1.2 Integers Versus Fractions                                                                                |

|   |        | 5.1.3 2s-Complement Arithmetic                                                                                 |

|   |        | 5.1.4 Extended-Precision 2s-Complement Arithmetic                                                              |

|   | 5.2    | Extended-Precision Addition and Subtraction 5-10                                                               |

|   | 5.3    | Extended-Precision Multiplication 5-17                                                                         |

|   | 5.4    | Division 5-21                                                                                                  |

|   |        | 5.4.1 Integer Division 5-21                                                                                    |

|   |        | 5.4.2 Fractional Division 5-30                                                                                 |

|   | 5.5    | Methods of Handling Overflows                                                                                  |

| 6 | Bit-R  | eversed Addressing 6-1                                                                                         |

|   | Introd | duces bit-reverse addressing and its implementation on the TMS320C55x DSP. Includes examples.                  |

|   | 6.1    | Introduction to Bit-Reverse Addressing                                                                         |

|   | 6.2    | Using Bit-Reverse Addressing In FFT Algorithms                                                                 |

|   | 6.3    | In-Place Versus Off-Place Bit-Reversing                                                                        |

|   | 6.4    | Using the C55x DSPLIB for FFTs and Bit-Reversing 6-8                                                           |

| 7 | Appli  | ication-Specific Instructions                                                                                  |

|   | Expla  | nins how to implement some common DSP algorithms using specialized TMS320C55x intions. Includes code examples. |

|   | 7.1    | Symmetric and Asymmetric FIR Filtering (FIRS, FIRSN)                                                           |

|   |        | 7.1.1 Symmetric FIR Filtering With the firs Instruction                                                        |

|   |        | 7.1.2 Antisymmetric FIR Filtering With the firsh Instruction                                                   |

|   |        | 7.1.3 Implementation of a Symmetric FIR Filter on the TMS320C55x DSP 7-4                                       |

|   | 7.2    | Adaptive Filtering (LMS) 7-6                                                                                   |

|   |        | 7.2.1 Delayed LMS Algorithm 7-7                                                                                |

|   | 7.3    | Convolutional Encoding (BFXPA, BFXTR)                                                                          |

|   |        | 7.3.1 Bit-Stream Multiplexing and Demultiplexing                                                               |

|   | 7.4    | Viterbi Algorithm for Channel Decoding (ADDSUB, SUBADD, MAXDIFF) 7-16                                          |

| 8 | TI C5  | 5x DSPLIB                                                                         | 8-1 |

|---|--------|-----------------------------------------------------------------------------------|-----|

|   | Introd | duces the features and the C functions of the TI TMS320C55x DSP function library. |     |

|   | 8.1    | Features and Benefits                                                             | 8-2 |

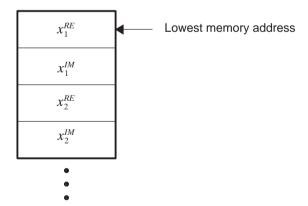

|   | 8.2    | DSPLIB Data Types                                                                 | 8-2 |

|   | 8.3    | DSPLIB Arguments                                                                  | 8-2 |

|   | 8.4    | Calling a DSPLIB Function from C                                                  | 8-3 |

|   | 8.5    | Calling a DSPLIB Function from Assembly Language Source Code                      | 8-4 |

|   | 8.6    | Where to Find Sample Code                                                         |     |

|   | 8.7    | DSPLIB Functions                                                                  | 8-5 |

|   |        | 8.7.1 Description of Arguments                                                    | 8-5 |

|   |        | 8.7.2 List of DSPLIB Functions                                                    | 8-5 |

## **Figures**

| 1–1 | Code Development Flow                                                                          | 1-3  |

|-----|------------------------------------------------------------------------------------------------|------|

| 2–1 | Section Allocation                                                                             |      |

| 2-2 | Extended Auxiliary Registers Structure (XARn)                                                  |      |

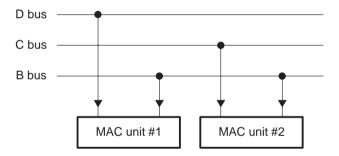

| 4–1 | Data Bus Usage During a Dual-MAC Operation                                                     |      |

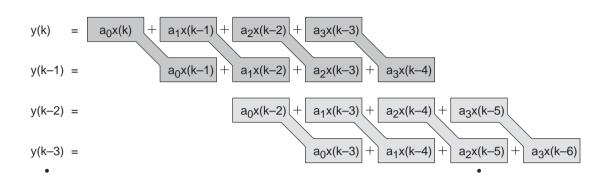

| 4–2 | Computation Groupings for a Block FIR (4-Tap Filter Shown)                                     |      |

| 4–3 | Computation Groupings for a Single-Sample FIR With an Even Number of TAPS (4-Tap Filter Shown) |      |

| 4–4 | Computation Groupings for a Single-Sample FIR With an Odd Number of TAPS (5-Tap Filter Shown)  |      |

| 4–5 | Matrix to Find Operators That Can Be Used in Parallel                                          |      |

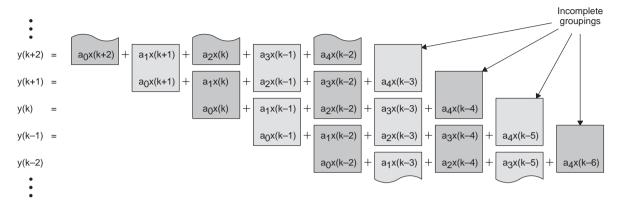

| 4–6 | CPU Operators and Buses                                                                        |      |

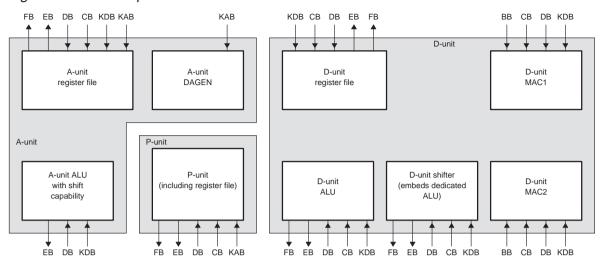

| 4–7 | Process for Applying User-Defined Parallelism                                                  | 4-27 |

| 4–8 | Second Segment of the Pipeline (Execution Pipeline)                                            | 4-53 |

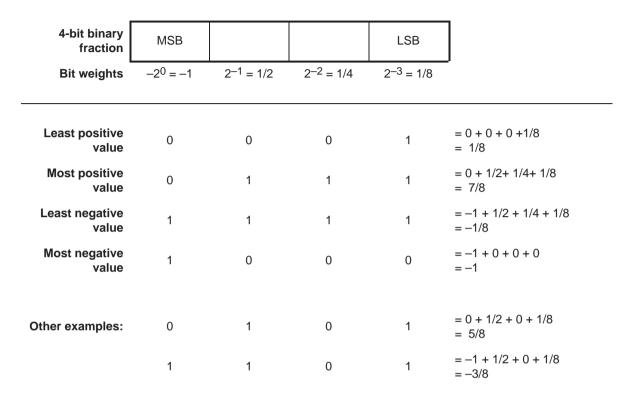

| 5–1 | 4-Bit 2s-Complement Integer Representation                                                     | 5-4  |

| 5–2 | 8-Bit 2s-Complement Integer Representation                                                     | 5-4  |

| 5–3 | 4-Bit 2s-Complement Fractional Representation                                                  | 5-5  |

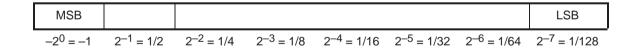

| 5–4 | 8-Bit 2s-Complement Fractional Representation                                                  | 5-5  |

| 5-5 | 32-Bit Addition                                                                                | 5-11 |

| 5–6 | 32-Bit Subtraction                                                                             | 5-14 |

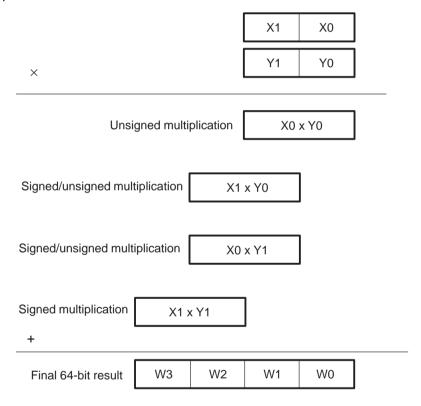

| 5–7 | 32-Bit Multiplication                                                                          | 5-17 |

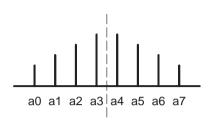

| 6–1 | FFT Flow Graph Showing Bit-Reversed Input and In-Order Output                                  | 6-4  |

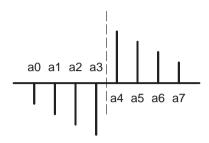

| 7–1 | Symmetric and Antisymmetric FIR Filters                                                        | 7-3  |

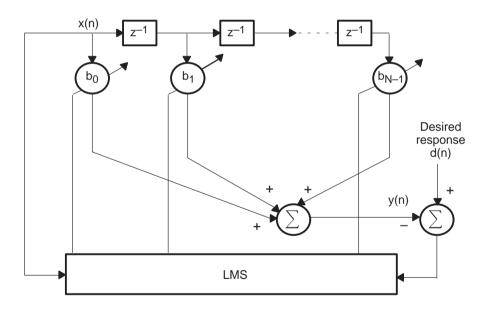

| 7–2 | Adaptive FIR Filter Implemented With the Least-Mean-Squares (LMS) Algorithm                    | 7-6  |

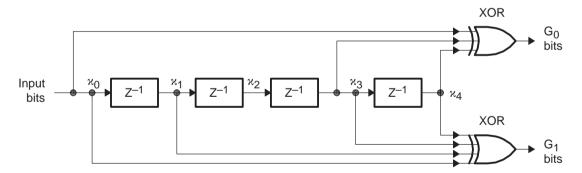

| 7–3 | Example of a Convolutional Encoder                                                             | 7-10 |

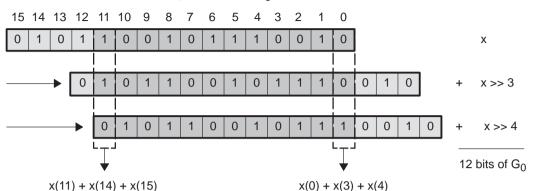

| 7–4 | Generation of an Output Stream G0                                                              | 7-11 |

| 7–5 | Bit Stream Multiplexing Concept                                                                |      |

| 7–6 | Butterfly Structure for K = 5. Rate 1/2 GSM Convolutional Encoder                              | 7-17 |

## **Tables**

| 3–1  | Compiler Options Summary                                                                                                      | 3-2  |

|------|-------------------------------------------------------------------------------------------------------------------------------|------|

| 3–2  | TMS320C55x C Compiler Intrinsics                                                                                              |      |

| 3–3  | Section Descriptions                                                                                                          |      |

| 3–4  | Possible Operand Combinations                                                                                                 |      |

| 4–1  | CPU Data Buses and Constant Buses                                                                                             |      |

| 4–2  | Basic Parallelism Rules                                                                                                       |      |

| 4–3  | Advanced Parallelism Rules                                                                                                    |      |

| 4–4  | Steps in Process for Applying User-Defined Parallelism                                                                        |      |

| 4–5  | Descriptions of the Execution Pipeline Stages                                                                                 |      |

| 4–6  | Recommendations for Preventing Pipeline Delays                                                                                |      |

| 4–7  | Status Register Pipeline-Protection Granularity                                                                               |      |

| 4–8  | MMR Pipeline-Protection Granularity                                                                                           | 4-66 |

| 4–9  | Half-Cycle Accesses to Dual-Access Memory (DARAM)                                                                             | 4-78 |

| 4–10 | One-Cycle Accesses to Single-Access Memory (SARAM)                                                                            | 4-79 |

| 4–11 | Cross-Reference Table Documented By Software Developers to Help Software Integrators Generate an Optional Application Mapping | 4-81 |

| 6–1  | Syntaxes for Bit-Reverse Addressing Modes                                                                                     |      |

| 6–2  | Bit-Reversed Addresses                                                                                                        | 6-3  |

| 6–3  | Typical Bit-Reverse Initialization Requirements                                                                               | 6-5  |

| 7–1  | Operands to the firs or firsh instruction                                                                                     | 7-4  |

| 8–1  | DSPLIB Function Argument Descriptions                                                                                         | 8-5  |

| 8–2  | DSPLIB Functions                                                                                                              | 8-6  |

## **Examples**

| 2–1  | Final Assembly Code of test.asm                                         | 2-4  |

|------|-------------------------------------------------------------------------|------|

| 2–2  | Partial Assembly Code of test.asm (Step 1)                              | 2-6  |

| 2–3  | Partial Assembly Code of test.asm (Step 2)                              | 2-7  |

| 2–4  | Partial Assembly Code of test.asm (Part3)                               |      |

| 2–5  | Linker command file (test.cmd)                                          | 2-11 |

| 2–6  | Linker map file (test.map)                                              | 2-12 |

| 2–7  | x Memory window                                                         | 2-17 |

| 3–1  | Main Function File                                                      | 3-6  |

| 3–2  | Sum Function File                                                       | 3-6  |

| 3–3  | Assembly Code Generated With -o3 and -pm Options                        | 3-7  |

| 3–4  | Assembly Generated Using -o3 -pm and -oi50                              | 3-11 |

| 3–5  | Implementing Saturated Addition in C                                    | 3-12 |

| 3–6  | Assembly Code Generated by C Implementation of Saturated Addition       | 3-13 |

| 3–7  | Single Call to _sadd Intrinsic                                          | 3-13 |

| 3–8  | Assembly code Generated When Using Compiler Intrinsic for Saturated Add | 3-14 |

| 3–9  | Block Copy Using Long Data Access                                       | 3-16 |

| 3–10 | Simple Loop that Allows Use of Local Repeat                             | 3-17 |

| 3–11 | Assembly Code for Local Repeat Generated by the Compiler                | 3-18 |

| 3–12 | Inefficient Loop Code for Loop Variable and Constraints (C)             | 3-19 |

| 3–13 | Inefficient Loop Code for Variable and Constraints(Assembly)            | 3-20 |

| 3–14 | Using Unsigned Data Types                                               | 3-20 |

| 3–15 | Assembly Code Generated for Unsigned Data Type                          | 3-21 |

| 3–16 | Using _nassert Directive                                                | 3-22 |

| 3–17 | Assembly Code Generated With _nassert Directive                         | 3-22 |

| 3–18 | Main Function Calling sum                                               | 3-24 |

| 3–19 | Assembly Code Generated With Main Calling sum                           | 3-25 |

| 3–20 | Assembly Source Output Using -o3 and -pm Options                        | 3-26 |

| 3–21 | Use Local Rather Than Global Summation Variables                        | 3-28 |

| 3–22 | Returning Q15 Result for Multiply Accumulate                            | 3-29 |

| 3–23 | Simulating Circular Addressing in C                                     | 3-30 |

| 3–24 | Assembly Output for Circular Addressing C Code                          | 3-31 |

| 3–25 | Circular Addressing Using Modulus Operator                              | 3-32 |

| 3–26 | Assembly Output for Circular Addressing Using Modulo                    | 3-33 |

| 3–27 | Considerations for Long Data Objects in Structures                      | 3-34 |

| 3–28 | Declaration Using DATA_SECTION Pragma                                   | 3-37 |

| 3–29 | Sample Linker Command File                                              | 3-39 |

|      |                                                                         |      |

| 3–30 | Allocation of Functions Using CODE_SECTION Pragma                                                          | 3-40 |

|------|------------------------------------------------------------------------------------------------------------|------|

| 4–1  | Complex Vector Multiplication Code                                                                         | 4-7  |

| 4–2  | Block FIR Filter Code (Not Optimized)                                                                      | 4-12 |

| 4–3  | Block FIR Filter Code (Optimized)                                                                          | 4-14 |

| 4–4  | A-Unit Code With No User-Defined Parallelism                                                               | 4-30 |

| 4–5  | A-Unit Code in Example 4–4 Modified to Take Advantage of Parallelism                                       | 4-33 |

| 4–6  | P-Unit Code With No User-Defined Parallelism                                                               | 4-35 |

| 4–7  | P-Unit Code in Example 4–6 Modified to Take Advantage of Parallelism                                       | 4-37 |

| 4–8  | D-Unit Code With No User-Defined Parallelism                                                               |      |

| 4–9  | D-Unit Code in Example 4–8 Modified to Take Advantage of Parallelism                                       | 4-39 |

| 4–10 | Code That Uses Multiple CPU Units But No User-Defined Parallelism                                          | 4-40 |

| 4–11 | Code in Example 4–10 Modified to Take Advantage of Parallelism                                             |      |

| 4–12 | Nested Loops                                                                                               |      |

| 4–13 | Branch-On-Auxiliary-Register-Not-Zero Construct (Shown in Complex FFT Loop Code)                           | 4-48 |

| 4–14 | Use of CSR (Shown in Real Block FIR Loop Code)                                                             |      |

| 4–15 | A-Unit Register Write/(Read in AD Stage) Sequence                                                          |      |

| 4–16 | A-Unit Register Read/(Write in AD Stage) Sequence                                                          |      |

| 4–17 | Register (Write in X Stage)/(Read in R Stage) Sequence                                                     |      |

| 4–18 | Good Use of MAR Instruction (Write/Read Sequence)                                                          |      |

| 4–19 | Bad Use of MAR Instruction (Read/Write Sequence)                                                           |      |

| 4–20 | Solution for Bad Use of MAR Instruction (Read/Write Sequence)                                              |      |

| 4–21 | ST0_55 Course Granularity                                                                                  |      |

| 4–22 | ST0_55 Fine Granularity                                                                                    |      |

| 4–23 | MMR Coarse Granularity                                                                                     |      |

| 4–24 | MMR Fine Granularity                                                                                       |      |

| 4–25 | Protected BRC Read                                                                                         |      |

| 4–26 | Unprotected BRC Read                                                                                       |      |

| 4–27 | Unprotected BRC Write                                                                                      |      |

| 4–28 | BRC Initialization                                                                                         |      |

| 4–29 | CSR Initialization                                                                                         |      |

| 4–30 | Condition Evaluation Preceded by a X-stage Write to the Register Affecting the Condition                   |      |

| 4–31 | Making an Operation Conditional With execute(AD_unit)                                                      |      |

| 4–32 | Making an Operation Conditional With execute(D_unit)                                                       |      |

| 4–33 | Conditional Parallel Write Operation Followed by an AD-Stage Write to the Register Affecting the Condition |      |

| 4–34 | Write/Dual-Operand Read Sequence                                                                           |      |

| 7 07 | (Assumes Xmem, Ymem, and Smem Are in the Same SARAM block)                                                 | 4-82 |

| 5–1  | Signed 2s-Complement Binary Number Expanded to Decimal Equivalent                                          |      |

| 5–2  | Computing the Negative of a 2s-Complement Number                                                           |      |

| 5–3  | Addition With 2s-Complement Binary Numbers                                                                 |      |

| 5–4  | Subtraction With 2s-Complement Binary Numbers                                                              |      |

| 5–5  | Multiplication With 2s-Complement Binary Numbers                                                           |      |

| 5–6  | 64-Bit Addition                                                                                            |      |

| 5–7  | 64-Bit Subtraction                                                         | 5-15 |

|------|----------------------------------------------------------------------------|------|

| 5–8  | 32-Bit Integer Multiplication                                              | 5-18 |

| 5–9  | 32-Bit Fractional Multiplication                                           | 5-20 |

| 5–10 | Unsigned, 16-Bit By 16-Bit Integer Division                                | 5-22 |

| 5–11 | Unsigned, 32-Bit By 16-Bit Integer Division                                | 5-23 |

| 5–12 | Signed, 16-Bit By 16-Bit Integer Division                                  | 5-26 |

| 5–13 | Signed, 32-Bit By 16-Bit Integer Division                                  | 5-28 |

| 6–1  | Sequence of Auxiliary Registers Modifications in Bit-Reversed Addressing . | 6-2  |

| 6–2  | Off-Place Bit Reversing of a Vector Array (in Assembly)                    | 6-6  |

| 6–3  | Using DSPLIB cbrev() Routine to Bit Reverse a Vector Array (in C)          | 6-8  |

| 7–1  | Symmetric FIR Filter                                                       | 7-5  |

| 7–2  | Delayed LMS Implementation of an Adaptive Filter                           | 7-9  |

| 7–3  | Generation of Output Streams G0 and G1                                     | 7-11 |

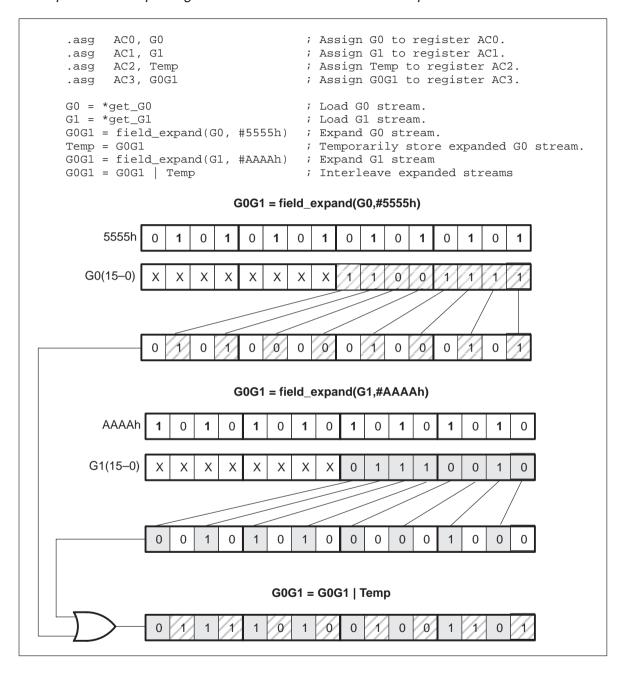

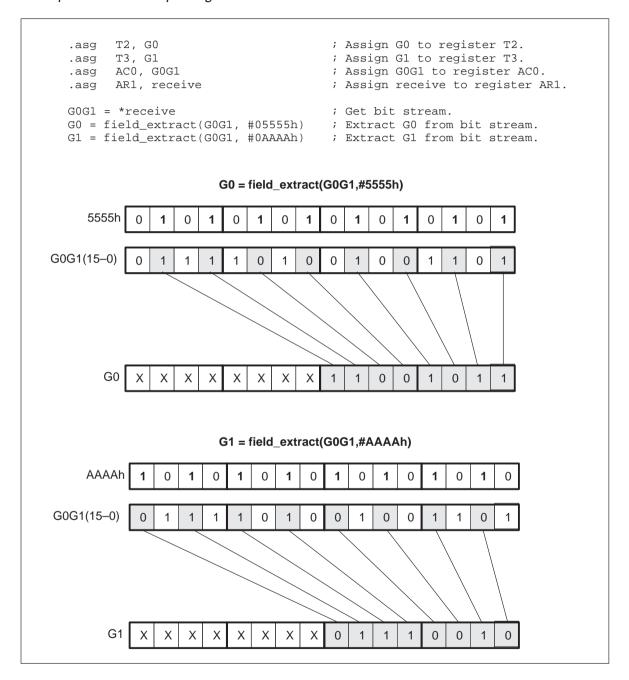

| 7–4  | Multiplexing Two Bit Streams With the Field Expand Instruction             | 7-13 |

| 7–5  | Demultiplexing a Bit Stream With the Field Extract Instruction             | 7-15 |

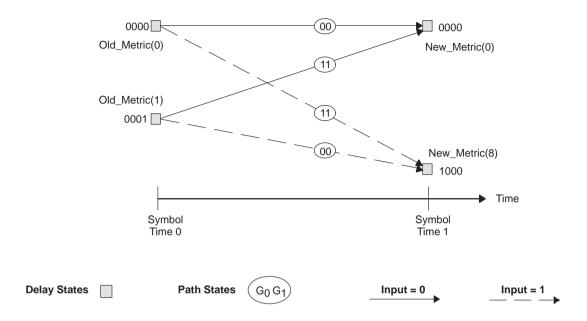

| 7–6  | Viterbi Butterflies for Channel Coding                                     | 7-19 |

| 7_7  | Viterhi Butterflies Using Instruction Parallelism                          | 7-21 |

## Chapter 1

## Introduction

This chapter lists some of the key features of the TMS320C55 $x^{\text{TM}}$  (C55 $x^{\text{TM}}$ ) DSP architecture and shows a recommended process for creating code that runs efficiently.

| Topic | c Pa <sub>s</sub>                            | ge |

|-------|----------------------------------------------|----|

| 1.1   | TMS320C55x Architecture                      | -2 |

| 1.2   | Code Development Flow for Best Performance 1 | -3 |

#### 1.1 TMS320C55x Architecture

main block of the DSP is the central processing unit (CPU), which has the following characteristics: ☐ A unified program/data memory map. In program space, the map contains 16M bytes that are accessible at 24-bit addresses. In data space, the map contains 8M words that are accessible at 23-bit addresses An input/output (I/O) space of 64K words for communication with peripherals. ☐ Software stacks that support 16-bit and 32-bit push and pop operations. You can use these stack for data storage and retreival. The CPU uses these stacks for automatic context saving (in response to a call or interrupt) and restoring (when returning to the calling or interrupted code sequence). A large number of data and address buses, to provide a high level of parallelism. One 32-bit data bus and one 24-bit address bus support instruction fetching. Three 16-bit data buses and three 24-bit address buses are used to transport data to the CPU. Two 16-bit data buses and two 24-bit address buses are used to transport data from the CPU. An instruction buffer and a separate fetch mechanism, so that instruction fetching is decoupled from other CPU activities. The following computation blocks: one 40-bit arithmetic logic unit (ALU), one 16-bit ALU, one 40-bit shifter, and two multiply-and-accumulate units (MACs). In a single cycle, each MAC can perform a 17-bit by 17-bit multiplication (fractional or integer) and a 40-bit addition or subtraction with optional 32-/40-bit saturation. An instruction pipeline that is protected. The pipeline protection mechanism inserts delay cycles as necessary to prevent read operations and write operations from happening out of the intended order. Data address generation units that support linear, circular, and bit-reverse addressing. ☐ Interrupt-control logic that can block (or mask) certain interrupts known as the maskable interrupts. ☐ A TMS320C54x-compatible mode to support code originally written for a TMS320C54x<sup>TM</sup> DSP.

The TMS320C55x device is a fixed-point digital signal processor (DSP). The

#### 1.2 Code Development Flow for Best Performance

The following flow chart shows how to achieve the best performance and codegeneration efficiency from your code. After the chart, there is a table that describes the phases of the flow.

Figure 1–1. Code Development Flow

From Step 2 (previous page) Identify time-critical portions of C code Step 3: Write Assembly Write them in assembly code Code Profile Yes Efficient Done enough? No Optimize assembly code Step 4: Optimize 4 Assembly Profile Code No Efficient enough? Yes Done

Figure 1–1. Code Development Flow (Continued)

#### Goal Step 1 Write C Code: You can develop your code in C using the ANSIcompliant C55x C compiler without any knowledge of the C55x DSP. Use Code Composer Studio to identify any inefficient areas that you might have in your C code. After making your code functional, you can improve its performance by selecting higher-level optimization compiler options. If your code is still not as efficient as you would like it to be, proceed to step 2. 2 Optimize C Code: Explore potential modifications to your C code to achieve better performance. Some of the techniques you can apply include (see Chapter 3): Use specific types (register, volatile, const). Modify the C code to better suit the C55x architecture. Use an ETSI intrinsic when applicable. ☐ Use C55x compiler intrinsics. After modifying your code, use the C55x profiling tools again, to check its performance. If your code is still not as efficient as you would like it to be, proceed to step 3. 3 Write Assembly Code: Identify the time-critical portions of your C code and rewrite them as C-callable assembly-language functions. Again, profile your code, and if it is still not as efficient as you would like it to be, proceed to step 4. 4 Optimize Assembly Code: After making your assembly code functional, try to optimize the assembly-language functions by using some of the techniques described in Chapter 4, Optimizing Your Assembly Code. The techniques include:

Rewrite or reorganize code to avoid pipeline protection delays.

Place instructions in parallel.

☐ Minimize stalls in instruction fetching.

## **Chapter 2**

## **Tutorial**

This tutorial walks you through the code development flow introduced in Chapter 1, and introduces you to basic concepts of TMS320C55x<sup>TM</sup> (C55x<sup>TM</sup>) DSP programming. It uses step-by-step instructions and code examples to show you how to use the software development tools integrated under Code Composer Studio (CCS).

Installing CCS before beginning the tutorial allows you to edit, build, and debug DSP target programs. For more informatiopn about CCS features, see the CCS Tutorial. You can access the CCS Tutorial within CCS by choosing Help→Tutorial→CCS Tutorial.

The examples in this tutorial were run on the CCS v1.2 software development tools, the most recent version available as of the publication of this book. Because the tools are being continuously improved, you may get different results if you are using a more recent version of the tools. The examples use instructions from the algebraic instruction set, but the concepts apply equally for the mnemonic instruction set.

| Topi | c Pag                             | е |

|------|-----------------------------------|---|

| 2.1  | Introduction                      | 2 |

| 2.2  | Writing Assembly Code2-3          | 3 |

| 2.3  | Understanding the Linking Process | ) |

| 2.4  | Building Your Program 2-14        | 1 |

| 2.5  | Testing Your Code                 | ô |

| 2.6  | Benchmarking Your Code 2-18       | 3 |

#### 2.1 Introduction

This tutorial presents a simple assembly code example that adds four numbers together (y = x0 + x3 + x1 + x2). This example helps you become familiar with the basics of C55x programming.

After completing the tutorial, you should know:

The four common C55x addressing modes and when to use them.

The basic C55x tools required to develop and test your software.

This tutorial does not replace the information presented in other C55x documentation and is not intended to cover all the topics required to program the C55x efficiently.

Refer to the related documentation listed in the preface of this book for more information about programming the C55x DSP. Much of this information has been consolidated as part of the C55x Code Composer Studio online help.

For your convenience, all the files required to run this example can be downloaded with the .PDF version of the *TMS320C55x Programmer's Guide* (*SPRU376*) from http://www.ti.com/sc/docs/schome.htm.

#### 2.2 Writing Assembly Code

| vvri | ting your assembly code involves the following steps:                                                                                                                                                  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Allocate sections for code, constants, and variables.                                                                                                                                                  |

|      | Initialize the processor mode.                                                                                                                                                                         |

|      | Set up addressing modes and add the following values: $x0 + x1 + x2 + x3$ .                                                                                                                            |

| The  | e following rules should be considered when writing C55x assembly code:                                                                                                                                |

|      | Labels                                                                                                                                                                                                 |

|      | The first character of a label must be a letter or an underscore ( _ ) followed by a letter, and must begin in the first column of the text file. Labels can contain up to 32 alphanumeric characters. |

|      | Comments                                                                                                                                                                                               |

|      | When preceded by a semicolon ( ; ), a comment may begin in any column. When preceded by an asterisk ( $^{\star}$ ), a comment must begin in the first column.                                          |

The final assembly code product of this tutorial is displayed in Example 2–1, Final Assembly Code of test.asm. This code performs the addition of the elements in vector x. Sections of this code are highlighted in the three steps used to create this example.

For more information about assembly syntax, see the *TMS320C55x Assembly Language Tools User's Guide*.

#### Example 2-1. Final Assembly Code of test.asm

```

* Step 1: section allocation

* _____

.def x,y,init

; reserve 4 uninitalized 16-bit locations for x

; reserve 1 uninitialized 16-bit location for y

.usect "vars",4

.usect "vars",1

; create initialized section "table" to

.sect "table"

; contain initialization values for x

init .int 1,2,3,4

; create code section (default is .text)

.text

.def start

; define label to the start of the code

start

* Step 2: Processor mode initialization

bit(ST1, #ST1 C54CM) = #0; set processor to '55x native mode instead of

'54x compatibility mode (reset value)

bit(ST2, #ST2_AROLC) = #0 ; set ARO register in linear mode

bit(ST2, #ST2_AR6LC) = #0 ; set AR6 register in linear mode

* Step 3a: copy initialization values to vector x using indirect addressing

сору

XAR0 = #x

; XARO pointing to variable x

XAR6 = #init

; XAR6 pointing to initialization table

*AR0+ = *AR6+

; copy starts from "init" to "x"

*AR0+ = *AR6+

*AR0+ = *AR6+

*AR0 = *AR6

* Step 3b: add values of vector x elements using direct addressing

add

XDP = \#x

; XDP pointing to variable x

; and the assembler is notified

.dp x

AC0 = @x

AC0 += @(x+3)

AC0 += @(x+1)

AC0 += @(x+2)

* Step 3c. write the result to y using absolute addressing

*(#y) = AC0

end

nop

goto end

```

#### 2.2.1 Allocate Sections for Code, Constants, and Variables

The first step in writing this assembly code is to allocate memory space for the different sections of your program.

Sections are modules consisting of code, constants, or variables needed to successfully run your application. These modules are defined in the source file using assembler directives. The following basic assembler directives are used to create sections and initialize values in the example code.

|                                                                           | .sect "section_name" creates initialized name section for code/data. Initialized sections are sections defining their initial values.                                                                                                     |  |  |  |  |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                           | .usect "section_name", size creates uninitialized named section for data. Uninitialized sections declare only their size in 16-bit words, but do not define their initial values.                                                         |  |  |  |  |

|                                                                           | .int <i>value</i> reserves a 16-bit word in memory and defines the initialization value                                                                                                                                                   |  |  |  |  |

|                                                                           | .def <i>symbol</i> makes a symbol global, known to external files, and indicates that the symbol is defined in the current file. External files can access the symbol by using the .ref directive. A symbol can be a label or a variable. |  |  |  |  |

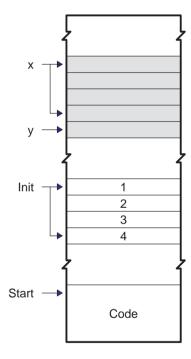

|                                                                           | shown in Example 2–2 and Figure 2–1, the example file test.asm contains ee sections:                                                                                                                                                      |  |  |  |  |

|                                                                           | vars, containing five uninitialized memory locations.                                                                                                                                                                                     |  |  |  |  |

|                                                                           | $\blacksquare$ The first four are reserved for vector $x$ (the input vector to add).                                                                                                                                                      |  |  |  |  |

|                                                                           | ■ The last location, <i>y</i> , will be used to store the result of the addition.                                                                                                                                                         |  |  |  |  |

|                                                                           | <i>table</i> , to hold the initialization values for <i>x</i> . The <i>init</i> label points to the beginning of section <i>table</i> .                                                                                                   |  |  |  |  |

|                                                                           | text, which contains the assembly code.                                                                                                                                                                                                   |  |  |  |  |

| Example 2–2 shows the partial assembly code used for allocating sections. |                                                                                                                                                                                                                                           |  |  |  |  |

#### Example 2–2. Partial Assembly Code of test.asm (Step 1)

```

* Step 1: section allocation

* ----

.def x,y,init

x .usect "vars",4 ; reserve 4 uninitalized locations for var x

y .usect "vars",1 ; reserve 1 uninitialized location for result y

.sect "table" ; create initialized section "table" to

init .int 1,2,3,4 ; contain initialization values for x

.text ; create code section (default is .text)

.def start ; make the start label global

start ; define label to the start of the code

```

Figure 2-1. Section Allocation

#### 2.2.2 Processor Mode Initialization

The second step is to make sure the status registers (ST0\_55, ST1\_55, ST2\_55, and ST3\_55) are set to configure your processor. You will either need to set these values or use the default values. Default values are placed in the registers after processor reset. You can locate the default register values after reset in the *TMS320C55x DSP CPU Reference Guide (SPRU371)*.

As shown in Example 2-3:

```

☐ The AR0 and AR6 registers are set to linear addressing (instead of circular addressing) using bit addressing mode to modify the status register bits. The syntax for bit addressing mode is:

```

bit (register, #register\_bitname)=#0 or #1

☐ The processor has been set in C55x native mode instead of C54x-compatible mode.

#### Example 2-3. Partial Assembly Code of test.asm (Step 2)

#### 2.2.3 Setting up Addressing Modes

Four of the most common C55x addressing modes are used in this code:

ARn Indirect addressing (identified by \*), in which you use auxiliary registers (ARx) as pointers.

DP direct addressing (identified by @), which provides a positive offset addressing from a base address specified by the DP register. The offset is calculated by the assembler and defined by a 7-bit value embedded in the instruction.

k23 absolute addressing (identified by #), which allows you to specify the entire 23-bit data address with a label.

Bit addressing (identified by the bit instruction), which allows you to modify a single bit of a memory location or MMR register.

For further details on these addressing modes, refer to the *TMS320C55x DSP CPU Reference Guide (SPRU371)*. Example 2–4 demonstrates the use of the addressing modes discussed in this section.

In Step 3a, initialization values from the *table* section are copied to vector x (the vector to perform the addition) using indirect addressing. Figure 2–2 illustrates the structure of the extended auxiliar registers (XARn). The XARn register is used only during register initialization. Subsequent operations use ARn because only the lower 16 bits are affected (ARn operations are restricted to a 64k main data page). AR6 is used to hold the address of *table*, and AR0 is used to hold the address of x.

In Step 3b, direct addressing is used to add the four values. Notice that the XDP register was initialized to point to variable *x*. The .dp assembler directive is used to define the value of XDP, so the correct offset can be computed by the assembler at compile time.

Finally, in Step 3c, the result was stored in the y vector using absolute addressing. Absolute addressing provides an easy way to access a memory location without having to make XDP changes, but at the expense of an increased code size.

#### Example 2-4. Partial Assembly Code of test.asm (Part3)

```

* Step 3a: copy initialization values to vector x using indirect addressing

сору

XAR0 = #x

; XARO pointing to startn of x array

XAR6 = #init

; XAR6 pointing to start of init array

*AR0+ = *AR6+

; copy from source "init" to destination "x"

*AR0+ = *AR6+

*AR0+ = *AR6+

*AR0 = *AR6

* Step 3b: add values of vector x elements using direct addressing

add

; XDP pointing to variable x

XDP = #x

; and the assembler is notified

.dp x

AC0 = @x

AC0 += @(x+3)

AC0 += @(x+1)

AC0 += @(x+2)

* Step 3c. write the result to y using absolute addressing

*(#y) = AC0

end

nop

goto end

```

Figure 2–2. Extended Auxiliary Registers Structure (XARn)

|              | 22–16         | 15–0        |

|--------------|---------------|-------------|

| XAR <i>n</i> | AR <i>n</i> H | AR <i>n</i> |

**Note:** ARnH (upper 7 bits) specifies the 7-bit main data page. ARn (16-bit registers) specifies a 16-bit offset to the 7-bit main data page to form a 23-bit address.

#### 2.3 Understanding the Linking Process

The linker (lnk55.exe) assigns the final addresses to your code and data sections. This is necessary for your code to execute.

The file that instructs the linker to assign the addresses is called the linker command file (test.cmd) and is shown in Example 2–5. The linker command file syntax is covered in detail in the *TMS320C55x Assembly Language Tools User's Guide (SPRU280)*.

- All addresses and lengths given in the linker command file uses byte addresses and byte lengths. This is in contrast to a TMS320C54x™ linker command file that uses 16-bit word addresses and word lengths.

The MEMORY linker directive declares all the physical memory available in your system (For example, a DARAM memory block at location 0x100 of length 0x8000 bytes). Memory blocks cannot overlap.

The SECTIONS linker directive lists all the sections contained in your input files and where you want the linker to allocate them.

The following linker options are used in Example 2–5:

- -o filename: names the executable file

- -m: creates a map file

- -e entry\_label: provides the entry point for the code

When you build your project in Section 2.4, this code produces two files, test.out and a test.map. Review the test.map file, Example 2–6, to verify the addresses for x, y, and table. Notice that the linker reports byte addresses for program labels such as *start* and *text*, and 16-bit word addresses for data labels like x, y, and *table*. The C55x DSP uses byte addressing to access variable length instructions. Instructions can be 1-6 bytes long.

#### Example 2–5. Linker command file (test.cmd)

```

test.obj    /* input files */

-o test.out    /* output file */

-m test.map    /* map file */

-e start    /* entry point for the code */

MEMORY    /* byte address, byte len */

{

DARAM: org= 000100h, len = 8000h

SARAM: org= 010000h, len = 8000h

}

SECTIONS    /* byte address, byte len */

{

vars :> DARAM

table: > SARAM

.text:> SARAM

}

```

#### Example 2–6. Linker map file (test.map)

| TMS320C5           | 5xx COF                    | F Linker                                 | Versi       | on 1.03B   |           | *******                            |

|--------------------|----------------------------|------------------------------------------|-------------|------------|-----------|------------------------------------|

| OUTPUT F           |                            | E: <test.ou<br>BOL: "start"</test.ou<br> |             | 0010008    |           |                                    |

| MEMORY C           | ONFIGUR.                   |                                          |             |            |           |                                    |

|                    | name<br><br>DARAM<br>SARAM | org (bytes<br><br>00000100<br>00010000   |             |            | <br>00a F | ttributes fill<br><br>RWIX<br>RWIX |

| SECTION            | ALLOCAT                    | ION MAP                                  |             |            |           |                                    |

| output<br>section  | page                       | orgn(bytes)                              | orgn(words) | len(bytes) | len(words | attributes/<br>s) input sections   |

| vars               | 0                          |                                          | 00000080    |            | 00000005  | UNINITIALIZED test.obj (vars)      |

| table              | 0                          |                                          | 00008000    |            | 00000004  | 04 test.obj                        |

| (table) .text      | 0                          | 00010008<br>00010008                     |             | 00000038   |           | test.obj                           |

| (.text)<br>= 2020] |                            | 0001003f                                 |             | 00000001   |           | HOLE [fill                         |

| .data              | 0                          |                                          | 00000000    |            | 0000000   | UNINITIALIZED 00 test.obj          |

| (.data)            | 0                          |                                          | 00000000    |            | 0000000   | UNINITIALIZED 00 test.obj (.bss)   |

#### Example 2–6. Linker map file (test.map), (Continued)

```

GLOBAL SYMBOLS: SORTED ALPHABETICALLY BY Name

abs. value/

byte addr word addr name

____

00000000 .bss

00000000 .data

00010008

.text

00000000

___bss___

___data__

0000000

0000000

___edata__

00000000

____end___

00010040

___etext__

00010008

___text__

00000000 edata

00000000 end

00010040

etext

0008000

init

00010008

start

08000000

Х

00000084

У

GLOBAL SYMBOLS: SORTED BY Symbol Address

abs. value/

byte addr word addr name

_____

-----

____

00000000

___end__

00000000 ___edata__

00000000 end

00000000 edata

00000000 ___data__

00000000

.data

.bss

00000000

____bss___

00000000

00000080 x

00000084

У

0008000

init

00010008

start

00010008

.text

00010008

___text_

___etext__

00010040

00010040

etext

[16 symbols]

```

#### 2.4 Building Your Program

At this point, you should have already successfully installed CCS and selected the C55x Simulator as the CCS configuration file to be used. You can select a configuration file to be used in CCS Setup.

Before building your program, you must set up your work environment and create a .mak file. Setting up your work environment involves the following tasks:

|   | Creating a project             |

|---|--------------------------------|

|   | Adding files to the work space |

|   | Modifying the build options    |

| _ | Building your program          |

#### 2.4.1 Creating a Project

First, create a new project called test.mak.

- 1) From the Project menu, choose New.

- Navigate to c:\ti\myprojects\55x\_examples\55x\_prog.

- Create the folder named 55x\_prog if needed.

- 4) In the File Name field, Type tutor.mak and select Save.

- 5) You have now created a project named tutor.mak and saved it in c:\ti\my-projects\55x\_examples\55x\_prog

#### 2.4.2 Adding Files to the Work space

Copy the tutorial files (test.asm and test.cmd) to the project directory.

- 1) Navigate to the directory where the tutorial files are located.

- Copy the tutorial files and paste them into the project directory you created earlier: c:\ti\myprojects\55x\_examples\55x\_prog

As an alternative, you can create your own source files by choosing File—New—Source File and typing the source code from the examples in this book.

#### 2.4.3 Modifying Build Options

#### Open the options dialog box and modify the Assebler and Linker options

- 1) From the Project menu, choose Options.

- 2) Select the Assembler tab.

- 3) Select Algebraic as the Assembler Type.

- 4) Select the Linker tab.

- 5) In the Map Filename field, type test.map.

- 6) In the Autoinitialization Model field, select No Autoinitialization.

#### 2.4.4 Build the Program

#### From the Project menu, choose Rebuild All

-x: Exaustively Read Libraries

When you build your project, CCS compiles, assembles, and links your code in one step. The assembler reads the assembly source file and converts C55x instructions to their corresponding binary encoding. The results of the assembly processes are an object file, *test.obj*, in industry standard COFF binary format. The object file contains all of your code and variables, but the addresses for the different sections of code are not assigned. This assignment takes place during the linking process.

Because there is no c code in your project, no compiler options were used.

The following basic assembler options were used to build the program:

|    | -as: Include symbols, make all symbols global                    |

|----|------------------------------------------------------------------|

|    | -g: Enables assembly source debug                                |

|    | -mg: Defines the assembler type as Algebraic                     |

| Th | e following basic linker options were used to build the program: |

|    | -m: Map filename                                                 |

|    | -o: Output filename                                              |

#### 2.5 Testing your code

To test your code, inspect its execution using the C55x Simulator.

#### Load test.out

- 1) From the File menu, choose Load program.

- 2) Navigate to and select test.out, then choose Open.

CCS now displays the test.asm source code at the beginning of the start label because of the entry symbol defined in the linker command file (-e start). Otherwise, it would have shown the location pointed to by the reset vector. You can also define the start location under the Project Options Linker tab.

#### Display arrays x, y, and init by setting Memory Window options

- 1) From the View menu, chose Memory.

- 2) In the Title field, type x.

- In the Address field, type x.

- 4) Repeat 1–3 for v.

- 5) Display the *init* array by selecting View→ Memory.

- In the Title field, type Table.

- 7) In the Address field, type init.

- 8) Display AC0 by selecting View→CPU Registers→CPU Registers.

The labels x, y, and *init* are visible to the simulator (using View $\rightarrow$  Memory) because they were exported as symbols (using the .def directive in test.asm). The -g option was used to enable assembly source debugging.

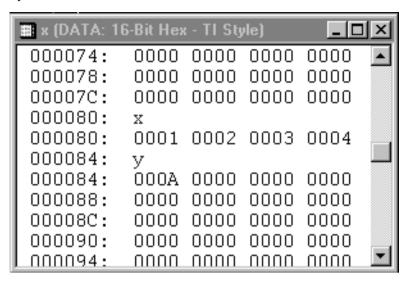

Now, single-step through the code to the *end* label by selecting Debug $\rightarrow$ Step Into. Examine the X Memory window to verify that the table values populate x and that y gets the value 0xa (1 + 2 + 3 + 4 = 10 = 0xa), as shown in Example 2–7.

Example 2–7. x Memory window

## 2.6 Benchmarking your code

After verifying the correct functional operation of your code, you can use CCS to calculate the number of cycles your code takes to execute.

#### Reload your code

From the File menu, choose Reload Program.

#### Enable clock for profiling

- 1) From the Profiler menu, choose Enable clock.

- 2) From the Profiler menu, choose View Clock.

#### Set breakpoints

- 1) Select the *test.asm* window.

- Set one breakpoint at the beginning of the code you want to benchmark: Right-click on the instruction next to the *copy* label and choose *Toggle Breakpoint*.

- 3) Set one breakpoint marking the end: Right-click on the instruction next to the *end* label and choose *Toggle Breakpoint*.

#### Benchmark your code

- 1) Run to the first breakpoint by selecting Debug→ Run.

- 2) Double-click in the *Clock window* to clear the cycle count.

- Run to the second breakpoint by selecting Debug→ Run.

- 4) The *Clock window* displays the number of cycles the code took to execute between the breakpoints, which was 15.

## **Chapter 3**

# **Optimizing C Code**

You can maximize C performance by using compiler options, intrinsics, and code transformations. The assembly-language examples in this chapter use instructions from the algebraic instruction set, but the concepts apply equally for the mnemonic instruction set.

| Topic Pag |                                                | Page  |

|-----------|------------------------------------------------|-------|

| 3.1       | The Compiler and Its Options                   | . 3-2 |

| 3.2       | Using Program-level Optimization               | . 3-5 |

| 3.3       | Using Function Inlining                        | 3-10  |

| 3.4       | Using Intrinsics                               | 3-12  |

| 3.5       | Using Long Data Accesses for 16 Bit Data       | 3-16  |

| 3.6       | Generating Efficient Loop Code                 | 3-17  |

| 3.7       | Generating Efficient Control Code              | 3-27  |

| 3.8       | Efficient Math Operations                      | 3-28  |

| 3.9       | Memory Management                              | 3-34  |

| 3.10      | Allocating Function Code to Different Sections | 3-40  |

## 3.1 The Compiler and Its Options

The TMS320C55x<sup>TM</sup> (C55x<sup>TM</sup>) C Compiler provides a wide range of options. Some of these options affect how your C source code is parsed (analyzed for syntactic and semantic conformance to ANSI C standards), others may select debug capabilities, such as generation of listing files (-pl), or insertion of symbolic debugging directives for runtime debug with Code Composer Studio (-g). This section focuses on that subset of compiler options which affect the compiler optimization phase. These options enable techniques that the compiler uses to generate more efficient assembly language than it does when no optimizations are selected.

#### **Compiler Options**

Options control the operation of the compiler. They can significantly affect the efficiency of the assembly source code generated by the compiler when translating your C source. The following subset of available compiler options provide the overall best performance boost in terms of cycle count and code size reduction in the translated assembly.

Table 3–1. Compiler Options Summary

| Option |                    | Description                              |

|--------|--------------------|------------------------------------------|

| -x2    |                    | Enable inlining of inline functions      |

| -on    | n = 0<br>(default) | Simplifies control flow                  |

|        |                    | Allocates variables to registers         |

|        |                    | Performs loop rotation                   |

|        |                    | Eliminates unused code                   |

|        |                    | Simplifies expressions and statements    |

|        |                    | Expands calls to inline functions        |

|        | n = 1              | Same features as n=0 option PLUS:        |

|        |                    | Performs local copy/constant propagation |

|        |                    | Removes unused assignments               |

|        |                    | Eliminates local common expressions      |

|        | n = 2              | Same features as n=1 option PLUS:        |

|        |                    | Performs loop optimizations              |

|        |                    | Eliminates global common sub-expressions |

|        |                    | Eliminates global unused assignments     |

|        |                    | Performs loop unrolling                  |

Table 3–1. Compiler Options Summary (Continued)

| Option          |                    | Description                                                                                                                                                                                                                                          |

|-----------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | n = 3              | Same features as n=2 option PLUS:                                                                                                                                                                                                                    |

|                 |                    | Removes all functions that are never called.                                                                                                                                                                                                         |

|                 |                    | Simplifies functions with return values that are never used.                                                                                                                                                                                         |

|                 |                    | Inlines calls to small functions (regardless to declaration).                                                                                                                                                                                        |

|                 |                    | Reorders functions so that the attributes of a called function are known when the caller is optimized.                                                                                                                                               |

|                 |                    | Identifies file-level variable characteristics.                                                                                                                                                                                                      |

| –oi <i>size</i> |                    | Enables inlining of functions based on a maximum size. Size here is internally determined by the optimizer and does not correspond to bytes or any known standard unit. Use —onx to check sizes of individual functions.                             |

| -onx            | x= 0               | Disables optimizer information file (default).                                                                                                                                                                                                       |

|                 | x= 1               | Produces optimizer information file.                                                                                                                                                                                                                 |

|                 | x= 2               | Produces verbose optimizer information file.                                                                                                                                                                                                         |

| -op <i>n</i>    | n = 0              | Specifies that the code contains functions and variables which may be accessed by code outside of the source provided to the compiler and that the compiler should not remove them.                                                                  |

|                 | n = 1              | Specifies that the source code contains variables that are modified outside the module, but does not call any functions from outside the current source. The compiler should should not remove those variables.                                      |