# C54x-to-C55x Code Migration Reference Guide

### **Preliminary Draft**

This document contains preliminary data current as of the publication date and is subject to change without notice.

Literature Number: SPRU429 March 2001

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that products or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: <u>Standard Terms and Conditions of Sale for Semiconductor Products.</u> www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

#### **Preface**

### **Read This First**

#### About This Manual

This manual describes techniques for migrating code from a TMS320C54x<sup>™</sup> (C54x<sup>™</sup>) DSP to a TMS320C55x<sup>™</sup> (C55x<sup>™</sup>) DSP. It also describes techniques for optimizing your code during and after the migration.

This document uses the following conventions.

#### **Notational Conventions**

| The device number TMS320C55x is often abbreviated as C55x.                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| If an overbar is above the name of a signal (for example, $\overline{\text{BIO}}$ ), the signal is active low.                                 |

| Code examples are shown in a special typeface.                                                                                                 |

| In most cases, hexadecimal numbers are shown with the suffix h. For example, the following number is a hexadecimal 40 (decimal 64):            |

| 40h                                                                                                                                            |

| Similarly, binary numbers usually are shown with the suffix b. For example, the following number is the decimal number 4 shown in binary form: |

| 0100b                                                                                                                                          |

|                                                                                                                                                |

| Notation      | Description                  | Example                                                                 |

|---------------|------------------------------|-------------------------------------------------------------------------|

| Register(n-m) | Bits n through m of Register | AC0(15–0) represents the 16 least significant bits of the register AC0. |

| Bus[n:m]      | Signals n through m of Bus   | A[21:1] represents signals 21 through 1 of the external address bus.    |

☐ Bits and signals are sometimes referenced with the following notations:

| ☐ The following terms are used to name portions of o | f data: |

|------------------------------------------------------|---------|

|------------------------------------------------------|---------|

| Term   | Description            | Example                                 |

|--------|------------------------|-----------------------------------------|

| LSB    | Least significant bit  | In AC0(15-0), bit 0 is the LSB.         |

| MSB    | Most significant bit   | In AC0(15-0), bit 15 is the MSB.        |

| LSByte | Least significant byte | In AC0(15-0), bits 7-0 are the LSByte.  |

| MSByte | Most significant byte  | In AC0(15-0), bits 15-8 are the MSByte. |

| LSW    | Least significant word | In AC0(31-0), bits 15-0 are the LSW.    |

| MSW    | Most significant word  | In AC0(31–0), bits 31–16 are the MSW.   |

#### Related Documentation From Texas Instruments

The following books describe the TMS320C55x<sup>™</sup> (C55x<sup>™</sup>) DSP generation and related support tools. To obtain a copy of any of these TI documents, call the Texas Instruments Literature Response Center at (800) 477–8924. When ordering, please identify the book by its title and literature number.

TMS320C55x Technical Overview (literature number SPRU393). This overview is an introduction to the TMS320C55x<sup>™</sup> digital signal processor (DSP). The TMS320C55x is the latest generation of fixed-point DSPs in the TMS320C5000<sup>™</sup> DSP platform. Like the previous generations, this processor is optimized for high performance and low-power operation. This book describes the CPU architecture, low-power enhancements, and embedded emulation features of the TMS320C55x DSPs.

**TMS320C55x DSP CPU Reference Guide** (literature number SPRU371) describes the architecture, registers, and operation of the CPU for the TMS320C55x<sup>™</sup> digital signal processors (DSPs).

TMS320C55x DSP Peripherals Reference Guide (literature number SPRU317) describes the peripherals, interfaces, and related hardware that are available on TMS320C55x™ (C55x™) DSPs. It also describes how you can use software (idle configurations) to turn on or off individual portions of the DSP, so that you can manage power consumption.

TMS320C55x DSP Mnemonic Instruction Set Reference Guide (literature number SPRU374) describes the TMS320C55x™ DSP mnemonic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the algebraic instruction set.

- TMS320C55x DSP Algebraic Instruction Set Reference Guide (literature number SPRU375) describes the TMS320C55x™ DSP algebraic instructions individually. Also includes a summary of the instruction set, a list of the instruction opcodes, and a cross-reference to the mnemonic instruction set.

- **TMS320C55x Programmer's Guide** (literature number SPRU376) describes ways to optimize C and assembly code for the TMS320C55x<sup>™</sup> DSPs and explains how to write code that uses special features and instructions of the DSP.

- TMS320C55x Assembly Language Tools User's Guide (literature number SPRU280) describes the assembly language tools (assembler, linker, and other tools used to develop assembly language code), assembler directives, macros, common object file format, and symbolic debugging directives for TMS320C55x™ devices.

- TMS320C55x Optimizing C Compiler User's Guide (literature number SPRU281) describes the TMS320C55x™ C Compiler. This C compiler accepts ANSI standard C source code and produces assembly language source code for TMS320C55x devices.

- TMS320 Third-Party Support Reference Guide (literature number SPRU052) alphabetically lists over 100 third parties that provide various products that serve the TMS320™ DSP family. A myriad of products and applications are offered—software and hardware development tools, speech recognition, image processing, noise cancellation, modems, etc.

#### **Trademarks**

TMS320C5x, C5x, TMS320C54x, C54x, TMS320C55x, and C55x are trademarks of Texas Instruments.

All other trademarks are the property of their respective owners.

# **Contents**

| 1 | Intro | duction  |                                                                                                              | . 1-1 |

|---|-------|----------|--------------------------------------------------------------------------------------------------------------|-------|

|   | 1.1   |          | This Document                                                                                                |       |

|   | 1.2   |          | 54x-to-C55x Code Porting Process                                                                             |       |

|   | 1.3   |          | Performance to Expect in C54x Ported Code                                                                    |       |

|   |       | 1.3.1    | The Approach Selected When Porting Assembly Code                                                             |       |

|   |       | 1.3.2    | The Type of Assembly Code Being Ported                                                                       |       |

|   |       | 1.3.3    | The Mix of Assembly Code Versus C Code                                                                       |       |

| 2 | Phas  | e 1: Coo | de Re-assembly Using MASM55                                                                                  | . 2-1 |

|   | 2.1   |          | ew                                                                                                           |       |

|   | 2.2   |          | Dealing with Non-Portable Code                                                                               |       |

|   |       | 2.2.1    | Modify Code That Uses Hard-Coded Addresses and Offsets                                                       |       |

|   |       | 2.2.2    | Modify Code That Takes Advantage of the C54x Non-Protected Pipeline                                          | . 2-4 |

|   |       | 2.2.3    | Replace Code That Depends on the Condition of the C54x BIO Pin                                               | . 2-5 |

|   |       | 2.2.4    | Modify Code That Uses Reserved Symbols of the                                                                |       |

|   |       |          | C55x Code Generation Tools                                                                                   |       |

|   |       | 2.2.5    | Modify Code That Uses the ARP Register                                                                       |       |

|   | 2.3   |          | Porting System-Level Code                                                                                    |       |

|   |       | 2.3.1    | Add Code to Initialize the System Stack                                                                      |       |

|   |       | 2.3.2    | Rewrite the Interrupt Vector Table (IVT)                                                                     | . 2-9 |

|   |       | 2.3.3    | Rewrite Code That Initializes the Interrupt Vector Pointer (IPTR) in the PMST Register                       | 2-12  |

|   |       | 2.3.4    | Modify Code That Initializes the IMR and IFR Registers                                                       |       |

|   |       | 2.3.5    | Modify the Operands of the TRAP and INTR Instructions                                                        |       |

|   |       | 2.3.6    | Preserve MASM55 Temporary Register Values During Interrupt Service Routines                                  |       |

|   |       | 2.3.7    | Porting of C54x Peripheral and I/O Code to C55x DSPs                                                         |       |

|   |       | 2.3.8    | Use the C54x_CALL or C54x_FAR_CALL Pragma for C54x C-Callable Assembly Code                                  |       |

|   |       | 2.3.9    | Special Case: Instructions that use the Same AR for Xmem and Ymem and that Modify the AR in the Ymem operand |       |

|   |       | 2.3.10   | Change the Linker Command File                                                                               | 2-22  |

| 3 | Phase      | e 2: Selected Code Optimization of Medium MIPS Functions (Optional)                                | 3-1    |

|---|------------|----------------------------------------------------------------------------------------------------|--------|

|   | 3.1        | Overview                                                                                           |        |

|   | 3.2        | Step 1: Use MASM55 Selected Optimization Switches                                                  | 3-6    |

|   | 3.3        | Step 2: Use C55x Instructions Selectively in C54x Source Code                                      | 3-7    |

|   |            | 3.3.1 Replace RPT with RPTBLOCAL if MASM55 Translates the                                          |        |

|   |            | Repeated C54x Instruction into Multiple C55x Instructions                                          | 3-7    |

|   |            | 3.3.2 Replace RPTB or RPTBD with RPTBLOCAL When Possible                                           |        |

|   |            | 3.3.3 Rearrange Code to Reduce C55x Pipeline Stalls                                                |        |

|   |            | 3.3.4 Replace C54x ASM Load Instructions with Equivalent C55x Instructions                         |        |

|   |            | 3.3.5 Delete Useless NOPs                                                                          |        |

|   |            | 3.3.6 Remove Circular Addressing Symbol (%) When it is Not Necessary                               |        |

|   | 3.4        | Step 3: Use C55x Instruction-Level Parallelism with C54x Instructions                              |        |

|   | 3.5        | Step 4: Evaluate Whether the 32-Bit Stack Mode is Required                                         |        |

|   | 3.6        | Step 5: Code and Data Placement Considerations                                                     |        |

|   |            | 3.6.1 Indirect Addressing Considerations                                                           |        |

|   |            | 3.6.2 DP Direct Addressing Considerations                                                          |        |

|   |            | 3.6.3 SP (Stack) Direct Addressing                                                                 |        |

|   |            | 3.6.4 Dmad, Pmad, and *(lk) Addressing Considerations                                              |        |

|   |            | 3.0.5 Indirect Cally Branch Considerations                                                         | . 3-19 |

| 4 | Phas       | e 3: Code Optimization of High MIPS Functions via                                                  |        |

|   |            | Native Implementation (Optional)                                                                   | 4-1    |

|   | 4.1        | Overview                                                                                           |        |

|   | 4.2        | Safe C54x/C55x Context Swapping                                                                    |        |

|   |            | 4.2.1 Calling a C55x Native Function from C54x Code                                                |        |

|   | 4.0        | 4.2.2 Calling a C54x Routine from C55x Native Code                                                 |        |

|   | 4.3        | Dual MAC Optimizations                                                                             |        |

|   | 4.4        | Circular Addressing Optimization                                                                   |        |

|   |            | 4.4.1 Step 1: Load the Buffer Size Register                                                        |        |

|   |            | 4.4.2 Step 2: Tell the CPU to Modify the Pointer Circularly                                        |        |

|   | 1 E        | 4.4.3 Step 3: Load the Buffer Start Address Register and the Pointer  Optimal Loop Implementations |        |

|   | 4.5        | 4.5.1 Differences in End-of-Loop Label Positioning                                                 |        |

|   |            | 4.5.2 Use RPTB or RPTBLOCAL Instead of BANZ to                                                     | . 4-14 |

|   |            | Implement an Outer Loop                                                                            | 4-15   |

|   |            | 4.5.3 Use of RPTSUB and RPTADD Instructions                                                        | . 4-15 |

|   | 4.6        | Use of the A-Unit ALU .                                                                            |        |

|   | 4.7        | Use of the Additional Accumulators and T Registers                                                 |        |

|   | 4.8        | Use of Improved Dual Reads and Writes for Faster Data Movement                                     |        |

|   | 4.9        | Using the Less Restrictive xmem/ymem Addressing                                                    |        |

|   | 4.10       | Use of the Additional TC Bits                                                                      |        |

|   | 4.11       | Other Potential Optimizations                                                                      |        |

|   | D          | ·                                                                                                  |        |

| Α |            | rved Symbols of the TMS320C55x Code Generation Tools  Operand Modifiers                            |        |

|   | A.1<br>A.2 | Register Names and Other Special Operands                                                          |        |

|   | A.2<br>A.3 | Instruction Keywords                                                                               |        |

|   | A.3<br>A.4 | Status Register Bit Names                                                                          |        |

|   | <b>△.4</b> | Otatus Negistei Dit Names                                                                          | A-O    |

# Figures

| 1–1 | Flowchart of the C54x-to-C55x Code Porting Process     | 1-5 |

|-----|--------------------------------------------------------|-----|

| 1–2 | C-Compiler Benchmarks                                  | -10 |

| 1–3 | Effect of Migration on Code-Size in G.723 Code Porting | -11 |

| 2–1 | Formation of an Interrupt Vector Address               | -12 |

| 2–2 | TEMP_SAVE and TEMP_RESTORE Macros 2                    | -17 |

| 2–3 | Comparison of the VC5416 and VC5510 Memory Maps        | -24 |

## **Tables**

| 1–1 | C54x vs. C55x Code Porting Performance Average                          | 1-8  |

|-----|-------------------------------------------------------------------------|------|

| 1–2 | C54x Versus C55x Cycle Comparison in DSPLIB Code                        | 1-9  |

| 2–1 | Phase 1: Code Re-assembly Using MASM55                                  |      |

| 2–2 | MASM55 C54x Compatibility Context Requirements                          | 2-3  |

| 2–3 | Cases in Which C54x Code is Not Portable                                |      |

| 2–4 | Step 2: Porting System-Level Code                                       | 2-7  |

| 2–5 | Linker Section Mapping Restrictions for C54x Ported Code                | 2-22 |

| 3–1 | Phase 2: Selected Code Optimization of Medium MIPS Functions (Optional) | 3-2  |

| 4–1 | Differences Between C54x Compatibility Mode and C55x Native Mode        | 4-2  |

| 4–2 | New C55x Architectural Features to Use in C55x Native Coding            | 4-3  |

| 4–3 | Block FIR Example Benchmarks                                            | 4-8  |

|     |                                                                         |      |

# **Examples**

| 2–1  | C55x Native Code to Test a GPIO Pin (IO0 Pin)                    | 2-6  |

|------|------------------------------------------------------------------|------|

| 2–2  | C54x Software Counter Code (Original)                            |      |

| 2–3  | C54x Interrupt Vector Table                                      |      |

| 2–4  | C55x Interrupt Vector Table (After Manual Modification)          | 2-12 |

| 2–5  | C54x Linker Command File                                         | 2-13 |

| 2–6  | C55x Linker Command File                                         | 2-14 |

| 2–7  | Original C54x ISR                                                | 2-18 |

| 2–8  | ISR of Example 2–7 (After Manual Modification)                   | 2-18 |

| 2-9  | C54x McBSP 0 Initialization                                      |      |

| 2-10 | C55x McBSP 0 Initialization                                      | 2-20 |

| 3–1  | C54x Calling C Function (After Phase 1 Changes)                  | 3-3  |

| 3–2  | Original C54x FIR Assembly Function                              | 3-4  |

| 3–3  | Optimized C54x FIR Assembly Function (After Phase 2 Changes)     | 3-5  |

| 4–1  | Calling a C55x Native Function from C54x Code                    | 4-4  |

| 4–2  | Macros to Use When Calling a C55x Native Function from C54x Code | 4-5  |

| 4–3  | Calling a Ported C54x Function from Native C55x Code             | 4-5  |

| 4–4  | Macros to Use When Calling a C54x Function from C55x Code        | 4-6  |

| 4–5  | Native C55x FIR Assembly Function (Single MAC)                   | 4-8  |

| 4–6  | Native C55x FIR Assembly Function (Dual MAC)                     | 4-8  |

| 4–7  | C54x Implementation of a Circular Buffer                         | 4-10 |

| 4–8  | C55x Native Implementation of a Circular Buffer                  | 4-10 |

# Chapter 1

# Introduction

| Topic |                                                | Page |

|-------|------------------------------------------------|------|

| 1.1   | About This Document                            | 1-2  |

| 1.2   | The C54x-to-C55x Code Porting Process          | 1-3  |

| 1.3   | What Performance to Expect in C54x Ported Code | 1-6  |

#### 1.1 About This Document

This document provides code migration examples that illustrate the recommended C54x-to-C55x code porting process. This document complements but does not replace the code migration information contained in the *TMS320C55x Assembly Language Tools User's Guide* (SPRU280). SPRU280 includes the minimum steps required to run your C54x code on a C55x DSP and presents the software system-level issues that need to be addressed as part of the application code porting.

This document does not cover hardware migration or differences between the C54x and C55x peripherals and external memory interfaces. While performing a hardware system migration, you may want to consult the *TMS320C55x DSP CPU Reference Guide* (SPRU371) and the *TMS320VC5510 Fixed-Point Digital Signal Processor* data sheet (SPRS076).

#### 1.2 The C54x-to-C55x Code Porting Process

The TMS320C55x<sup>™</sup> (C55x<sup>™</sup>) DSPs are source compatible with the TMS320C54x<sup>™</sup> (C54x<sup>™</sup>) DSPs and are able to run C54x code, producing bit-exact results. Migration of C54x mnemonic code to C55x mnemonic code can be achieved with minimal user intervention through the use of the C55x mnemonic assembler, MASM55. MASM55 assembles both C54x and the new C55x native instruction. To take full advantage of the C55x architecture, manual code modification of medium/high MIPS functions using C55x native instructions is suggested.

The recommended approach to migrate a C54x application code to C55x is the partial native/code re-assembly approach described below. This should be seen as a recommendation not as the only possible code porting methodology.

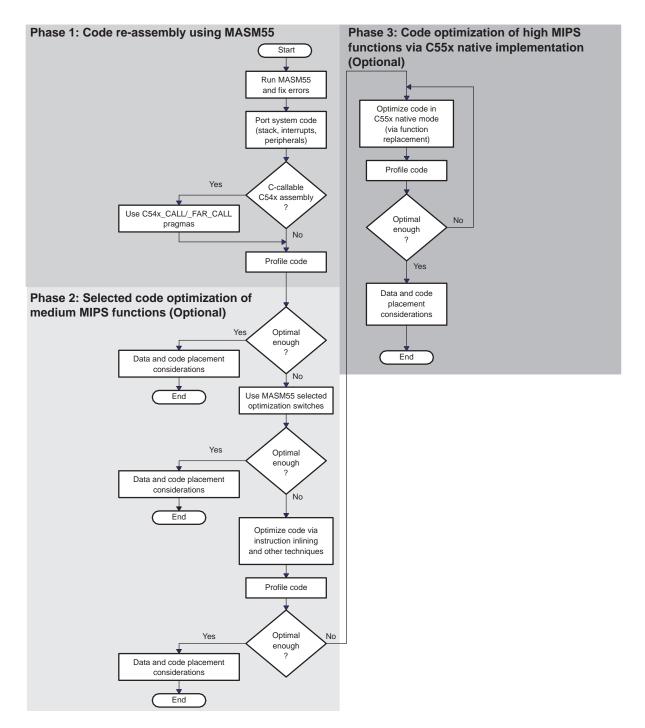

#### ☐ Phase 1: Code re-assembly using MASM55

The mnemonic C55x assembler (MASM55) can be used to port a C54x algorithm to the C55x. MASM55 assembles the C54x mnemonic source and produces C55x object code. This approach saves time as it requires minimal user intervention. The effort involved is typically independent of the size of the C54x code. User intervention may be required to:

- Port system level code: C54x and C55x are source compatible in terms of the CPU instruction set. However, C54x and C55x are different in their memory maps, peripherals, stack management, and interrupts. Manual modification of system initialization code may be required.

- Remove non-portable code: MASM55 will port all C54x code with few exceptions related to hard-coding of addresses and open pipeline tricks

#### ☐ Phase 2: Selected code optimization of medium MIPS functions (Optional)

The original C54x code does not exploit all the C55x architectural features. Limited code modification of the C54x medium MIPS functions is suggested to quickly get better cycle count and code size. For example, you can quickly make the C54x code more optimal by:

- Using MASM55 special optimization switches

- Using few C55x native instructions in your original C54x code

### ☐ Phase 3: Code optimization of high MIPS functions via C55x native implementation (Optional)

To optimize further, high MIPS consuming functions that could take advantage of the new C55x features should be implemented using C55x native instructions. The idea is to cycle profile all the functions and optimize a subset of the functions covering 80% of the algorithm MIPS. The reason is that in most applications, the high MIPS consuming modules represent only a small portion of the code size. Therefore, the effort is considerably less and the payback is substantial. However, the impact of new C55x architectural features, such as such as dual mac, dual store/load capability, nested block repeats and additional circular buffers, in those functions need to be analyzed to make a decision on native coding.

The C54x/C55x code porting process is illustrated in the flowchart presented in Figure 1–1. It is important to note that Phase 2 and Phase 3 steps are optional depending on your performance optimization goals. For example, you might be satisfied with the code performance that you obtain with just Phase 1, given the higher clock rate of C55x DSPs.

Figure 1–1. Flowchart of the C54x-to-C55x Code Porting Process

#### 1.3 What Performance to Expect in C54x Ported Code

The performance of C54x code ported to the C55x depends on 3 main factors:

- 1) The approach selected when porting assembly code

- 2) The type of assembly code being ported

- 3) The mix of assembly code versus C code

#### 1.3.1 The Approach Selected When Porting Assembly Code

There are three possible approaches when porting C54x assembly code to the C55x: code re-assembly using MASM55, a full C55x native coding approach, and a partial native/code re-assembly approach. In this document we recommend and cover the partial native/code re-assembly approach that is a mix of the other two approaches. However, it is important to decide on the approach with a clear understanding of the trade-offs involved.

Code re-assembly using MASM55 approach: A C54x mnemonic assembly implementation can be ported to the C55x by using the mnemonic C55x assembler (MASM55). MASM55 assembles the C54x mnemonic source and produces C55x object code. This approach corresponds to the Phase 1 of the C54x-to-C55x code porting process presented in this document.

#### **Advantages**

It is not a time consuming process and the effort involved is independent of the size of the C54x code being ported in most cases.

#### **Disadvantages**

- Manual code modification may be required to address differences between C54x and C55x in system-level code (interrupt and peripheral register initialization mostly)

- Masm55 does not exploit all the C55x architectural features and selected code modification may be required to get better cycle count and code size

#### **Expected Performance**

Table 1 shows a typical code size and cycle performance using the code re-assembly using MASM55 approach. After some of the C54x code optimization techniques presented in this document, **an average C54x/MASM55 ratio of 0.8 and 0.95 in cycle and code size respectively can be expected**. C55x performance have some degradation and for this reason this approach is typically recommended for less MIPS consuming functions.

|                         | wri                  | C55x native coding approach: This approach involves a code rete using C55x native instructions. This approach corresponds to the ase 3 of the C54x-to-C55x code porting process presented in this docunt. |  |

|-------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                         | Ad                   | vantages                                                                                                                                                                                                  |  |

|                         |                      | All architectural features of C55x can be exploited.                                                                                                                                                      |  |

|                         |                      | Developer has complete control over code size and cycles                                                                                                                                                  |  |

|                         | Dis                  | advantages                                                                                                                                                                                                |  |

| Time consuming process. |                      | ne consuming process.                                                                                                                                                                                     |  |

|                         | Expected Performance |                                                                                                                                                                                                           |  |

|                         |                      | ole 1–1 shows a typical code size and cycle performance using a full 5x native approach. <i>With this method an average C54x/ C55x ratio</i>                                                              |  |

full atio of 1.4 to 1.8 can be achieved depending on the type of code. The more MAC intensive the code is the better the ratio would be. Refer to this document and the TMS320C55x Programmer's Guide (SPR376) for recommended C55x programming techniques.

☐ Partial native/code re-assembly approach (Recommended Method): In C55x, it is possible to mix re-assembled C54x code with code using new C55x native instructions. Hence, to port an algorithm to the C55x, a mix of migrating techniques using MASM55 and native implementation can be used which can ensure quick migration with a good memory and MIPS performance gain.

#### **Advantages**

Enables the developer to exploit C55x new architectural features for MIPS intensive functions and quickly port the remaining less MIPS consuming functions via MASM55.

#### **Expected Performance**

Memory and cycle performance with this approach is application code specific. It depends on the code characteristics and on the mix of MASM55 re-assembled code versus C55x native code used. Table 1-1 shows that an average C54x/C55x cycle ratio of 1.35 to 1.6 can be achieved depending on the kind of code. The more MAC intensive the code is the better would be the ratio.

The use of MASM55 re-assembled code versus C55x native code should be decided on a function by function basis. The following recommendations apply when selecting what functions to implement in C55x native code:

- ☐ Functions that consume 80% of MIPS of the algorithm are good candidates for C55x native coding. The reason is that in most applications, the high MIPS consuming modules represent only a small portion of the code size. Therefore, the effort is considerably less and the payback is substantial. However, as explained below the type of operations in these functions needs also to be considered.

- □ The impact of new C55x architectural features on the function needs to be analyzed to make a decision on native coding. MIPS consuming functions that could take advantage of new C55x architectural features such as dual mac, dual store/load capability, nested block repeats and additional circular buffers are candidates for native coding. You can quickly make this analysis from the fixed-point C model of the algorithm if available.

In summary,

Partial native/code re-assembly approach following the 80% MIPS rule is the recommended method. Non-critical functions of the algorithm (less MIPS consuming functions) can be ported using MASM55 (with selected code changes) while the MIPS consuming functions can be implemented using C55x native instructions.

Table 1–1. C54x vs. C55x Code Porting Performance Average

|                                   | C54x/C55x Cycle Ratio | C54x/C55x Code Size Ratio         |

|-----------------------------------|-----------------------|-----------------------------------|

| MASM55                            | 0.8                   | 0.9–0.95                          |

| MASM55 with selected code changes | 0.9                   | 0.95                              |

| C55x Native                       | 1.4–1.8               | 0.95–1.1 (for DSP loop-type code) |

|                                   |                       | 1.25–1.3 (for control-type code)  |

| С                                 | not available         | 1.3–1.4                           |

**Note:** Larger means better performance for the C55x.

#### 1.3.2 The Type of Assembly Code Being Ported

A typical application consists of a mix of control code and DSP-loop code. Control code tends to dominate in size, while DSP-loop code tends to dominate in cycles. Therefore an optimal DSP processor architecture should concentrate on decreasing code size for control code and decreasing cycle count for DSP code. The C55x architecture was designed to achieve just that.

C55x control code will shrink in size compared with C54x control code, as seen in Table 1–1. Assembly code can get larger by 10-25% with DSP loop code because the C55x DSP generation offers a more powerful and orthogonal instruction set than the C54x DSP generation, and this requires more instruction encoding bits. This increase in code size is balanced by a decrease in cycle count, which can be seen in Table 1–2.

Table 1–2. C54x Versus C55x Cycle Comparison in DSPLIB Code

| Benchmark         | C55x Cycle Count | C54x Cycle Count |

|-------------------|------------------|------------------|

| Real block FIR    | nx/2 (4+nh)      | 4+nx(4+nh)       |

| complex block FIR | nx(2+ 2*nh)      | nx(13 + 8*nh)    |

| iircas4           | nx(5+4*nbiq)     | nx(11 + 4*nbiq)  |

| dlms kernel       | 5+ 2*nh          | 12 + 2*nh        |

| maxval            | nx               | 2*nx             |

- **Notes:** 1) nx = number of elements in the vector

- 2) nh = number of filter coefficients

- 3) nbiq = number of filter biquads

- 4) These kernels reflect a small subset of the C55x and C54x DSPLIB kernels. A complete set of C54x and C55x DSPLIB benchmarks can be found in the API descriptions in the Optimized DSP Library for C Programmers on the TMS320C54x (SPRA480) and the TMS320C55x DSP Library Programmer's Reference (SPRU422).

#### 1.3.3 The Mix of Assembly Code Versus C Code

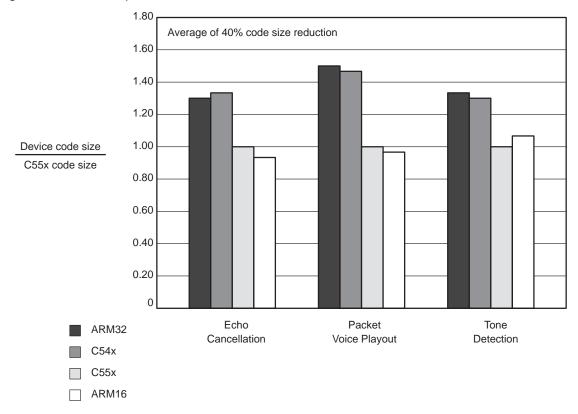

The C55x DSP generation has a more efficient compiler engine than the C54x DSP generation. Benchmarks on the C55x C compiler show a 30-40% code size reduction compared with those on the C54x C compiler (see Figure 1–2). The more C code your application has, the better code size and cycle improvements your ported code will see.

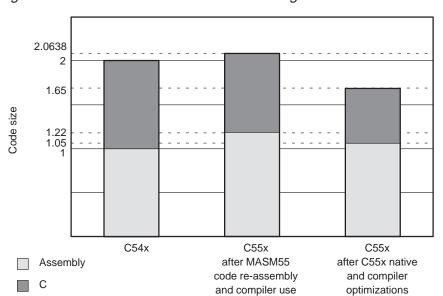

Combined C and assembly code usually gets smaller as shown in Figure 1–3, an example of a G.723 code porting. The analysis above assumes 50% C code, 50% assembly code and C54x code ported using MASM55 and the C55x compiler tools.

In Figure 1–3 (second bar), the G.723 assembly portion ported with MASM55 code re-assembly expanded by 22%, while the G.723 C portion shrunk by -21.67%, giving you an overall C-plus-assembly code growth of 6.38%.

Using C55x compiler optimization switches, the C code size can shrink to 30–40% of the C54x C code size. This is illustrated in Figure 1–3 (third bar).

Figure 1-2. C-Compiler Benchmarks

Figure 1-3. Effect of Migration on Code-Size in G.723 Code Porting

### Chapter 2

# Phase 1: Code Re-assembly Using MASM55

| Topi | c Pag                                      | е |

|------|--------------------------------------------|---|

| 2.1  | Overview                                   | 2 |

| 2.2  | Step 1: Dealing with Non-Portable Code 2-4 | 1 |

| 2.3  | Step 2: Porting System-Level Code          | 7 |

#### 2.1 Overview

The first Phase of the C54x-to-C55x code porting process is to achieve functional code using the C55x mnemonic assembler MASM55. MASM55 can port C54x mnemonic code to C55x with minimal user intervention. User intervention is required to:

☐ Address system-level issues such as differences in memory maps, peripherals, stack management, and interrupts

☐ Replace code that might not be portable

This chapter covers, in detail, these two steps. The steps are summarized in Table 2–1.

Table 2-1. Phase 1: Code Re-assembly Using MASM55

| STEP 1:<br>Dealing with Non-Portable Code |                                                                           | STEP 2:<br>Porting System-Level Code |                                                                                                                              |  |

|-------------------------------------------|---------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|

|                                           | Modify code that uses hard-coded                                          | Sta                                  | ck                                                                                                                           |  |

| _                                         | addresses and offsets.                                                    |                                      | Add code to initialize the system stack.                                                                                     |  |

|                                           | Modify code that takes advantage of the C54x non-protected pipeline.      | Inte                                 | errupts                                                                                                                      |  |

|                                           | Replace code that depends on the                                          |                                      | Rewrite the interrupt vector table (IVT).                                                                                    |  |

|                                           | condition of the C54x BIO pin.                                            |                                      | Rewrite code that initializes the interrupt vector pointer (IPTR).                                                           |  |

|                                           | Modify code that uses reserved symbols of the C55x code generation tools. |                                      | Modify code that initializes the IMR and IFR registers.                                                                      |  |

|                                           | Modify code that uses the ARP register.                                   |                                      | Modify the operands of the TRAP and INTR instructions.                                                                       |  |

| _                                         | modify code that account in the region.                                   |                                      | Preserve MASM55 temporary register values in nterrupt service routines.                                                      |  |

|                                           |                                                                           | Per                                  | ipherals                                                                                                                     |  |

|                                           |                                                                           |                                      | Rewrite code that accesses peripheral and EMIF (external memory interface) registers.                                        |  |

|                                           |                                                                           |                                      | Replace code that accesses the C54x I/O space.                                                                               |  |

|                                           |                                                                           | C-C                                  | Callable Assembly                                                                                                            |  |

|                                           |                                                                           |                                      | Use C54x_CALL/C54x_FAR_CALL pragmas for C54x C-callable assembly code.                                                       |  |

|                                           |                                                                           | Spe                                  | ecial Case                                                                                                                   |  |

|                                           |                                                                           |                                      | Inspect instructions that use the same auxiliary register (AR) for Xmem and Ymem and that modify the AR of the Ymem operand. |  |

|                                           |                                                                           | Lin                                  | ker Command File Changes                                                                                                     |  |

|                                           |                                                                           |                                      | Allocate the data stack and the system stack in the same 64K-word page.                                                      |  |

|                                           |                                                                           |                                      | Allocate all data in memory page 0 (the first 64K words of memory).                                                          |  |

|                                           |                                                                           |                                      | Make sure DP addressing arrays maintain the same C54x 128-word page boundary.                                                |  |

|                                           |                                                                           |                                      | Keep code being called by CALA in memory page 0 (the first 64K words of memory).                                             |  |

|                                           |                                                                           |                                      | Keep code reached by BACC in the same 64K-word page as the calling code.                                                     |  |

|                                           |                                                                           |                                      | Adjust for differences in the memory map and for byte addressing.                                                            |  |

To execute C54x code ported with MASM55 correctly, a C55x DSP needs to be in the C54x-compatible mode (C54CM = 1) and must meet all the associated conditions shown in Table 2–2. All of the conditions except the stack mode condition are the defaults forced by a DSP hardware reset. The stack mode is determined by the first byte of the reset vector, as described in the *TMS320C55x DSP CPU Reference Guide* (SPRU371).

Table 2-2. MASM55 C54x Compatibility Context Requirements

| Required Condition                                         | Description                                                                                                                                                                                                                     |  |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ST1(C54CM) = 1                                             | The C54x-compatible mode is enabled.                                                                                                                                                                                            |  |

| ST1(M40) = 0                                               | The D-unit of the CPU is in the 32-bit mode rather than the 40-bit mode.                                                                                                                                                        |  |

| ST2(ARMS) = 0                                              | C54x-compatible options are available for indirect addressing.                                                                                                                                                                  |  |

| ST2(RDM) = 0                                               | C54x-compatible rounding is used.                                                                                                                                                                                               |  |

| ST2(7-0) = 0                                               | Circular addressing is not forced for any of the auxiliary registers, AR0–AR7.                                                                                                                                                  |  |

| DPH = 0, $SPH = 0$ ,<br>AR0H-AR7H = 0,<br>CDPH = 0         | All data is accessed in the first 64K words of memory.                                                                                                                                                                          |  |

| BSA01 = 0, BSA23 = 0,<br>BSA45 = 0, BSA67 = 0,<br>BSAC = 0 | The C55x circular buffer start address registers are cleared so that they do not affect circular addressing.                                                                                                                    |  |

| Stack mode = 32-bit                                        | The data stack and the system stack act as a single 32-bit stack: When you access the data stack, the pointers for both stacks are modified by the same increment. The C55x fast-return registers (RETA and CFCT) are not used. |  |

#### 2.2 Step 1: Dealing with Non-Portable Code

Certain C54x instructions/code practices are not portable to the C55x DSPs. MASM55 flags most of these cases with "ERROR" or "REMARK" (indicating a weaker error), with the exception of open pipeline tricks. In this step, we must remove/replace those pieces of code to allow MASM55 to complete the C54x code assembly process.

Table 2–3 summarizes the cases in which C54x code is not portable, and the sections that follow the table describe how to handle such code.

Table 2-3. Cases in Which C54x Code is Not Portable

| Case                                             | Example    | MASM55 Behavior               |

|--------------------------------------------------|------------|-------------------------------|

| Hard-coded addresses/offsets (see section 2.2.1) | B #1233h   | REMARK                        |

| Open-pipeline tricking                           | LD #1, A   | REMARK (for XC)               |

| (see section 2.2.2)                              | XC 1, AEQ  | (Does not detect other cases) |

| BIO-pin-related code (see section 2.2.3)         | XC 1, BIO  | ERROR                         |

| New reserved symbols (see section 2.2.4)         | B \$       | ERROR                         |

| ARP-related code (see section 2.2.5)             | LD #3, ARP | ERROR                         |

#### 2.2.1 Modify Code That Uses Hard-Coded Addresses and Offsets

In C55x DSPs, addresses in program space are given in bytes, while those in C54x DSPs are given in words. Therefore, instructions that use hard-coded addresses/offsets (for example, #1000h) will not address the correct values, and for that reason, are flagged as MASM55 errors.

**WHAT TO DO:** It is good programming practice to avoid using hard-coded addresses or offsets. If hard-coded values have been used, replace them with labels so that the linker will resolve them at link time.

#### 2.2.2 Modify Code That Takes Advantage of the C54x Non-Protected Pipeline

The C54x instruction pipeline was not protected, and therefore had the potential to cause some out-of-order instruction execution. Although rarely done in practice, it was possible to take advantage of the open pipeline to save cycles.

As an example, consider the following C54x code. When the C54x CPU executes the XC (conditional execute) instruction, the content of accumulator A is sampled two cycles before the XC instruction is executed. Therefore, the action taken by the XC instruction depends on the LD instruction, not on the ADD instruction. Because the LD instruction makes the content of A equal to 0, the SUB instruction is executed.

```

LD 0, A

NOP

ADD #1, A

XC 1, AEQ

SUB #5, B

```

To make programming easier, each C55x DSP offers a protected pipeline to ensure in-order execution of instructions. In a C55x pipeline, the action taken by the XC instruction above would depend on the ADD instruction. As a result, the SUB instruction would *not* be executed.

**WHAT TO DO:** MASM55 *does not* detect the usage of all nonprotected pipeline cycles. For this reason, we suggest you pre-process your C54x assembly file by running the C54x assembly with the pipeline open detection enabled (asm500 –pw). However, be aware that asm500 –pw can detect only some open pipeline cases (not all).

#### 2.2.3 Replace Code That Depends on the Condition of the C54x BIO Pin

C54x devices have a BIO pin, but C55x devices do not. As a result, conditional instructions that test the condition of the  $\overline{\text{BIO}}$  pin cannot be ported to C55x devices. MASM55 flags an error in those cases.

**WHAT TO DO:** Change the C54x code that tests the  $\overline{\text{BIO}}$  pin to test something else, such as one of the pins of the C55x general-purpose I/O port (GPIO). Example 2–1 shows code that tests the C55x IO0 pin. Replacing the C54x  $\overline{\text{BIO}}$  code also means modifying the hardware design to use the newly chosen pin.

#### Example 2–1. C55x Native Code to Test a GPIO Pin (IO0 Pin)

```

i...

IODIR .set 0x3400

IODATA.set 0x3401

.text

start:

AND #0FFFEh, port(#IODIR); Configure IOO pin as input

MOV port(#IODATA), T3; Read GPIO data register into T3

AND #0001h, T3; Mask off all bits except the one for IOO

BCC start, T3 == 0; If T3=0 => IOO is low, goto start

i...

```

### 2.2.4 Modify Code That Uses Reserved Symbols of the C55x Code Generation Tools

C55x code generation tools use some new reserved symbols. Appendix A provides a list of the symbols.

**WHAT TO DO:** If your C54x code uses any reserved symbols, you must rename them.

#### 2.2.5 Modify Code That Uses the ARP Register

The ARP (auxiliary register pointer) of the TMS320C5x<sup>™</sup> and C54x DSPs is not supported in C55x DSPs.

**WHAT TO DO:** Unless you ported code from a C5x<sup>TM</sup> DSP to the C54x DSP, you should not be encountering this problem. If this issue does arise, you can replace ARP addressing with ARn addressing. For example if the code makes ARP = 3 and then uses \*+, you can remove the instruction that loads ARP and then replace \*+ with \*AR3+.

#### 2.3 Step 2: Porting System-Level Code

C55x DSPs are instruction source compatible with C54x DSPs. However, device differences related to interrupts, stack operation, peripherals, and memory mapping make code modification required to achieve fully functional application code.

Table 2–4 lists the steps required to make your code functional on a C55x DSP that is running under the conditions listed in Table 2–2. When you run MASM55, you will get REMARKs for some (but not all) of the issues presented in Table 2–4. To correct any of the issues mentioned in the table, manual inspection and code modification are required.

Most of the steps in Table 2–4 are illustrated through the software counter code of Example 2–2 (page 2-8). This simple example increments a low resolution counter until a certain value is reached and then triggers an interrupt to increment a high resolution counter.

Table 2-4. Step 2: Porting System-Level Code

| Cat  | egory                                                                                                            | MASM55<br>Behavior <sup>†</sup> | See            |  |  |

|------|------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------|--|--|

| Sta  | Stack                                                                                                            |                                 |                |  |  |

|      | Add code to initialize the system stack.                                                                         | REMARK                          | page 2-9       |  |  |

| Inte | errupts                                                                                                          |                                 |                |  |  |

|      | Rewrite the interrupt vector table (IVT).                                                                        | REMARK                          | Page 2-9       |  |  |

|      | Rewrite code that initializes the interrupt vector pointer (IPTR) in the PMST register.                          | REMARK                          | Page 2-12      |  |  |

|      | Modify code that initializes the IMR and IFR registers.                                                          | REMARK                          | Page 2-14      |  |  |

|      | Modify the operands of the TRAP and INTR instructions.                                                           | Does not detect                 | Page 2-15      |  |  |

|      | Preserve MASM55 temporary register values during interrupt service routines.                                     | REMARK on RETE instruction      | Page 2-16      |  |  |

| Pei  | Peripherals and I/O Space Accesses                                                                               |                                 |                |  |  |

|      | Rewrite code that accesses peripheral and EMIF registers.                                                        | REMARK                          | page 2-18      |  |  |

|      | Replace code that accesses the C54x I/O space.                                                                   | REMARK                          |                |  |  |

| C-C  | C-Callable Assembly                                                                                              |                                 |                |  |  |

|      | Use the C54x_CALL or C54x_FAR_CALL pragma for C54x C-callable assembly code.                                     | Does not detect                 | page 2-20      |  |  |

| Spe  | ecial Case                                                                                                       |                                 | Section 2.3.9, |  |  |

|      | Inspect instructions that use the same AR for Xmem and Ymem operands and that modify the AR in the Ymem operand. | REMARK                          | page 2-21      |  |  |

<sup>†</sup> MASM55 generates REMARK messages to flag most places in C54x code that require changes to make your code functional.

Table 2-4. Step 2: Porting System-Level Code (Continued)

| Car | tegory                                                                                       | MASM55<br>Behavior <sup>†</sup> | See             |  |

|-----|----------------------------------------------------------------------------------------------|---------------------------------|-----------------|--|

| Lin | ker Command File Changes                                                                     |                                 | Section 2.3.10, |  |

|     | Allocate the data stack and the system stack in same 64K-word page                           | -                               | page 2-22       |  |

|     | Allocate all data sections in memory page 0 (the first 64K words of memory)                  | -                               |                 |  |

|     | Allocate function code being called by CALA in memory page 0 (the first 64K words of memory) | -                               |                 |  |

|     | Allocate code reached by using BACC in the same 64K-word page as the calling code            | _                               |                 |  |

|     | Modify the interrupt vector table alignment requirement                                      | _                               |                 |  |

<sup>†</sup> MASM55 generates REMARK messages to flag most places in C54x code that require changes to make your code functional.

Example 2–2. C54x Software Counter Code (Original)

```

; . . .

start:

; Initialize stack pointer

; Clear all pending interrupts

#TOS, SP

#0FFFFh, IFR

STM

STM

; Disable interrupts

SSBX INTM

RSBX SXM

; Turn sign extension mode off

#RSV, A

; Load address of interrupt vector table

LD

into A

; Clear lower 7 bits of address

#0FF80h, A

AND

; (only upper 9 bits are needed for IPTR)

; . . .

OR

#0020h, A

; Set overlay bit

; Load PMST with result in A ; Load DP to point to lowent page ; Unmask SINT4 interrupt

STLM A, PMST

#lowcnt, DP

LD

#0010h, IMR

STM

RSBX INTM

; Enable interrupts

count_loop:

LD

lowcnt, A

; Load lowent into A

ADD

#1, A

; Add 1 to A

#1, A ; Add 1 to A

A, lowent ; Store A to lowent

#0500h, A ; Subtract 0x0500 from A

count_loop, ANEQ ; If (A != 0) goto count_loop

#0, lowent ; else, reset lowent

STL

SUB

#0500h, A

ВC

ST

INTR 20

; Trigger SINT4

count_loop

; Goto count_loop

```

#### 2.3.1 Add Code to Initialize the System Stack

#### Background

- ☐ Each C54x DSP has a single stack that is referenced by the 16-bit SP register. Each C55x DSP has an additional stack (the system stack) that is referenced by the 16-bit SSP register.

- □ In a C55x DSP, SP holds the 16 least significant bits (LSBs) of the 23-bit extended data stack pointer (XSP), and SSP holds the 16 LSBs of the 23-bit extended system stack pointer (XSSP). A single register, SPH, provides the 7 most significant bits (MSBs) of XSP and the 7 MSBs of XSSP. For that reason, both stacks must be located in the same 64K-word mepage of memory.

#### **Example: XSSP Initialization in the Software Counter Code**

It is important to initialize the system stack pointer in the software counter code (Example 2–2 on page 2-8) because the code calls an interrupt service routine (ISR) and thus will need to use the stacks to store and retreive data. The linker command file in Example 2–6 on page 2-14 shows how a section is allocated for the system stack on the same 64K-word page as the data stack. XSSP must be initialized to hold the address of this section. The modification for Example 2–2 is shown in the code below. Note that the write to XSSP loads a memory page into SPH, which is used for both stacks. Both stack memory sections can be placed on any page of data memory.

| Before (C54x) |          | After manual modification (C55x)     |

|---------------|----------|--------------------------------------|

| STM           | #TOS, SP | STM #TOS, SP  AMOV #TOSS, mmap(XSSP) |

**Note:** TOS = Top of (data) stack; TOSS = Top of system stack

#### 2.3.2 Rewrite the Interrupt Vector Table (IVT)

#### **Background**

☐ Interrupt vector locations: Both C54x and C55x devices have 32 interrupt vector locations, each consisting of eight bytes. In C54x DSPs the interrupt vector location includes a branch instruction to lead to the ISR. In C55x DSPs, the interrupt vector location includes the ISR address, and the CPU uses that address to branch to the ISR.

A C55x DSP ignores the first byte of each interrupt vector location except the reset vector location, whose first byte defines the stack mode. Use the .ivec directive supported by MASM55 to select the appropriate value for that first byte and to insert the 3-byte ISR address in the second, third, and fourth byte locations. If no instruction follows this, MASM55 inserts NOPs to fill the remaining bytes. However, you can insert one instruction within the fifth through eighth byte locations. Any second instruction in bytes 5 through 8 is ignored.

□ Rearranging interrupt vector locations: The interrupt vector offsets within the C55x interrupt vector table are different from those in a C54x DSP. For example, the INT0 vector is at word-offset 40h (byte-offset 0x80) in a C54x DSP but is at byte-offset 10h in a C55x DSP.

Also, a C55x DSP dedicates one interrupt vector to each peripheral event. There is no multiplexing of peripheral interrupt vectors like there is in C54x DSPs.

□ Relative priorities of interrupts: There is a difference between C54x and C55x interrupt priorities in some cases. For example in a C54x DSP, INT3 has a higher priority than the interrupt for McBSP 1. In a C55x DSP, the opposite is true. If ignored, the priority differences could have an unexpected impact on real-time systems.

#### **Example: Interrupt Vector Table for the Software Counter Code**

Example 2–3 and Example 2–4 show the C54x and C55x interrupt vector tables, respectively, for the software counter code (Example 2–2 on page 2-8). Note the use of the *.ivec* directive in the C55x version. Also, the size of the *.space* allocation and the parameters for *.loop* are different because of differences in the mapping of software interrupts within the vector table. The C54x interrupt vector for the RINTO/SINT4 ISR is at byte-offset A0h, but the corresponding VC5510 vector (for RINTO/SINT5) is at byte-offset 28h.

#### Example 2-3. C54x Interrupt Vector Table

```

; . . .

.sect "vectors"

; . . .

RSV: BD start ; Reset

NOP

NOP

; . . .

; Method 1: using .space

.space 16*4*19 ; 16 bits/word * 4 word/interrupt vector * 19 vector spaces

; Method 2: Using .loop and a dummy isr

; .loop 19 ; 19 "empty" vectors

bd dummy_isr

nop

nop

.endloop

; where dummy_isr could be defined as

.text

; dummy_isr

b dummy_isr

; Note: Use this dummy isr to detect and trap in code errors produced by

an unexpected interrupt vector fetch.

SINT4 BD SWI_4_isr ; Software Interrupt #4

NOP

NOP

; . . .

```

#### Example 2–4. C55x Interrupt Vector Table (After Manual Modification)

```

.sect "vectors"

RSV:

.ivec

; Reset

start

; Method 1: using .space

; 8 bits/byte * 8 bytes/interrupt vector * 4 vector spaces

.space 8*8*4

; Method 2: Using .loop and a dummy isr

; 4 "empty" vectors

.loop 4

.ivec dummy_isr

.endloop

; where dummy_isr could be defined as

.text

dummy_isr

b

dummy_isr

; Note: Use this dummy isr to detect and trap in code errors produced by

an unexpected interrupt vector fetch.

SWI 5 isr ; Software Interrupt #5

SINT5

.ivec

```

### 2.3.3 Rewrite Code That Initializes the Interrupt Vector Pointer (IPTR) in the PMST Register

#### **Background**

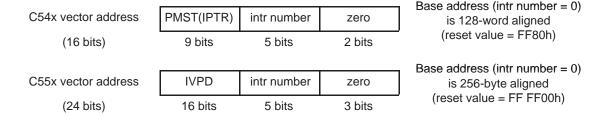

☐ The location of the interrupt vector table (IVT) after reset is word address FF80h in a C54x DSP and byte address FF FF00h in a C55x DSP. As shown in Figure 2–1, relocation of the IVT from its reset location is achieved by changing the value of the 9-bit PMST(IPTR) field in a C54x DSP and by changing the 16-bit IVPD (interrupt vector pointer-DSP) register in a C55x DSP. The "intr number" mentioned in the figure is the 5-bit binary number for the sequential position of the vector in the IVT. For example, the first vector in the IVT, the reset vector, is vector 0. Thus, for the reset vector, intr number = 0000b.

Figure 2–1. Formation of an Interrupt Vector Address

- ☐ The IVT alignment requirement stays the same: 128 16-bit words in a C54x DSP and the equivalent, 256 bytes, in a C55x DSP. However, because the C55x .align directive is given in bytes, we need to change the number used for the directive.

- ☐ A C55x device has separate host and DSP interrupt vector pointers (IVPH and IVPD) for the host and DSP interrupt vector tables, respectively, and they both need to be initialized if they are used. Special treatment is required when decoding with HPI-related interrupts.

#### Example: Initializing an Interrupt Vector Pointer in C55x Code

The C54x code that initializes PMST(IPTR) must be modified for C55x DSPs as shown below. Notice that in both the C54x case and the C55x case, a label (RSV) has been used for the reset vector address to avoid a hard-coded address. In the C55x code, the 24-bit address is shifted right by 8 bits so that the 16 MSBs are isolated and stored in IVPD (look back to Figure 2–1).

```

Before (C54x)

After (C55x)

STM #(RSV & OFF80h | 20h), PMST

MOV #(RSV >> 8), mmap(IVPD)

```

Compare the "vectors" section declarations in Example 2–5 (C54x code) and Example 2–6 (C55x code). Because C55x code is byte addressed, the interrupt vector table should be aligned on a 256-byte page (the 8 LSBs of the base address should be 0s). The linker command file in Example 2–6 reflects this fact by using the .align 256 directive rather than the .align 128 directive shown in Example 2–5.

#### Example 2–5. C54x Linker Command File

```

/* C54x Linker Command File

; . . .

SECTIONS

.text

:> PRAM

PAGE 0

vectors :> VECS PAGE 0, align 128 /* align given in words */

:> SPRAM PAGE 1

.bss

.data

:> DARAM PAGE 1

stack

:> DARAM PAGE 1

}

; . . .

```

#### Example 2-6. C55x Linker Command File

```

/* C55x Linker Command File

/*****************************

SECTIONS

.text

:> PRAM

vectors :> VECS, align 256 /* align now given in bytes */

.bss

:> SPRAM

:> DARAM

.data

stack

:> DARAM

sysstack :> DARAM

}

; . . .

```

#### 2.3.4 Modify Code That Initializes the IMR and IFR Registers

#### Background

A C54x DSP has two registers to flag and mask interrupts (IFR and IMR). To avoid the interrupt multiplexing done for peripherals in C54x DSPs, the C55x architecture expands the number of registers to four: two for flag bits (IFR0 and IFR1) and two for mask/enable bits (IER0 and IER1). In addition, relative bit locations for interrupts in the flag registers and mask/enable registers are different in C54x and C55x DSPs. Due to these differences, C54x code that initializes the interrupt registers must be rewritten.

#### **Example: Initializing Interrupt Registers in the Software Counter Code**

In the software counter code (Example 2–2 on page 2-8), all interrupt flags are cleared and only the interrupt SINT4 is left unmasked. The code below shows the modifications required for porting to a C55x device. The flags in both flag registers, IFR0 and IFR1, are cleared. The interrupt to be unmasked (corresponding to SINT4) is in IER0. Note that in Example 2–2, there was no need to unmask the interrupt because the IER0 bits do not affect the INTR instruction; it was done to show the changes required for a C55x DSP.

Note also that the value to be written to the IERs depends on how the interrupts are assigned to the bits in the IERs. Writing 0010h to IER0, as in the example, might not have the same effect as writing 0010h to IMR.

| Before (C54x) |              | After N | After Manual Modification (C55x) |  |

|---------------|--------------|---------|----------------------------------|--|

| STM           | #0FFFFh, IFR | MOV     | #0FFFFh, mmap(@IFR0)             |  |

|               |              | VOM     | #0FFFFh, mmap(@IFR1)             |  |

| STM           | #0010h, IMR  | VOM     | #0010h, mmap(@IER0)              |  |

|               |              | MOV     | #0000h, mmap(@IER1)              |  |

|               |              |         |                                  |  |

#### 2.3.5 Modify the Operands of the TRAP and INTR Instructions

C54x and C55x DSPs offer the same TRAP and INTR insruction mechanisms. However, due to the differences in the relative positions of the hardware interrupt vectors, you may need to modify the "K" operand value to avoid clashes between hardware and software interrupts (hardware and software interrupt tables overlap in both C54x and C55x devices). In the case of the software counter code (Example 2–2 on page 2-8), INTR 20 must be changed to INTR 5, as they both share the vector with RINTO.

#### Note:

MASM55 does not warn you that INTR/TRAP values may need to change. Manual inspection and code change is required.

## 2.3.6 Preserve MASM55 Temporary Register Values During Interrupt Service Routines

#### Background

□ A ported C54x interrupt service routine (ISR) needs to preserve on entry the following C55x registers, if they are used as temporary registers by MASM55 during the ISR assembly process. MASM55 uses temporary registers when one C54x instruction ports to more than one C55x instruction.

T1

AC2

AC3

XCDP

CSR

ST0\_55 (TC1 bit only)

ST2\_55

You must manually add code to your C54x ISR to preserve in the stack the C55x temporary registers used. Version 1.5 and later versions of MASM55 identify the temporary registers used by listing them at the top of the listing file. For example the listing file may have the following statement, indicating that you must preserve T1, AC2, AC3:

```

; Temporary Registers Used: AC2, AC3, T1.

```

In addition, the specific line of code that uses temporary registers is marked by *IREG!*. If looking in the listing files is troublesome, simply add the TEMP\_SAVE and TEMP\_RESTORE macros shown in Figure 2–2 at the beginning and at the end of the C54x ISR, to save and restore all of the possible temporary registers.

Figure 2–2. TEMP\_SAVE and TEMP\_RESTORE Macros

| TEMP_SAVE | .macro            | TEMP_RESTORE .macro |

|-----------|-------------------|---------------------|

|           | PSH mmap(@T1)     | POP map(@ST2_55)    |

|           | PSH dbl(AC2)      | POP mmap(@ST0_55)   |

|           | PSH dbl(AC3)      | POP mmap(@CSR)      |

|           | PSH mmap(@AC2G)   | POP mmap(@CDPH)     |

|           | PSH mmap(@AC3G)   | POP mmap(@CDP)      |

|           | PSH mmap(@CDP)    | POP mmap (@AC3G)    |

|           | PSH mmap(@CDPH)   | POP mmap(@AC2G)     |

|           | PSH mmap(@CSR)    | POP dbl(AC3)        |

|           | PSH mmap(@ST0_55) | POP dbl(AC2)        |

|           | PSH mmap(@ST2_55) | POP mmap(@T1)       |

|           | .endm             | .endm               |

|           |                   |                     |

□ In applications containing a mix of C54x and C55x instructions, if a C55x-native ISR uses MASM55 temporary registers, then the ISR must preserve on entry those registers. This would normally be done by the ISR, anyway, except in cases where one or more of these registers has been reserved for exclusive use by the ISR (not used in any other part of your code).

#### **Example: XCDP Used as a Temporary Register by MASM55**

In the software counter code (Example 2–2 on page 2-8), an INTR 20 instruction forces a branch to an ISR. The code for the ISR is shown in Example 2–7. When MASM55 assembles this ISR, there is one case of a multi-instruction porting that uses the XCDP register. An inspection of the ISR listing file reveals that XCDP is used as a temporary register in the porting of an MVDK instruction (XCDP is used because C55x DSPs do not support the C54x dmad type of addressing):

```

Before (C54x)

After MASM55 - Listing File

MVDK *(highent), #globent

AMOV #globent, XCDP

MOV *(highent), *CDP

```

The original XCDP value should be saved before XCDP is used in the ISR, and the original XCDP value should be restored before the CPU returns from the ISR. In preparation for another pass through MASM55, the ISR can be modified as shown in Example 2–8:

- ☐ Before the MVDK instruction, the modified ISR saves XCDP, by pushing its high part (CDPH) and its low part (CDP) onto the stack.

- □ Before ending, the modified ISR restores XCDP, by popping the two parts of XCDP off the stack.

#### Example 2-7. Original C54x ISR

```

SWI_4_isr:

; . . .

LD

highent, A

; load highent into A

#1, A

; add 1 to A

ADD

; store A to highcnt

STL

A, highcnt

; copy highent to globent

MVDK highcnt, #globcnt

; . . .

; return with interrupts enabled

RETE

```

#### Example 2–8. ISR of Example 2–7 (After Manual Modification)

```

SWI_5_isr:

i . . .

PSH

mmap(CDPH)

; save CDPH (upper 7 bits)

; save CDP (lower 16 bits)

PSH

mmap(CDP)

highent, A

; load highent into A

LD

ADD

#1, A

; add 1 to A

A, highcnt

; store A to highcnt

STL

MVDK highent, #globent

; copy highent to globent

; . . .

POP

mmap(CDP)

; restore CDP (lower 16 bits)

POP

mmap(CDPH)

; restore CDPH (upper 7 bits)

RETE

; return with interrupts enabled

```

#### 2.3.7 Porting of C54x Peripheral and I/O Code to C55x DSPs

#### **Background**

C54x code that initializes or controls peripherals cannot be ported correctly to a C55x device by MASM55. The same is true for C54x code that accesses I/O space. You must re-write the code because:

- ☐ The peripheral registers in a C55x device are located in the I/O space, while in a C54x device, they are located in the data space.