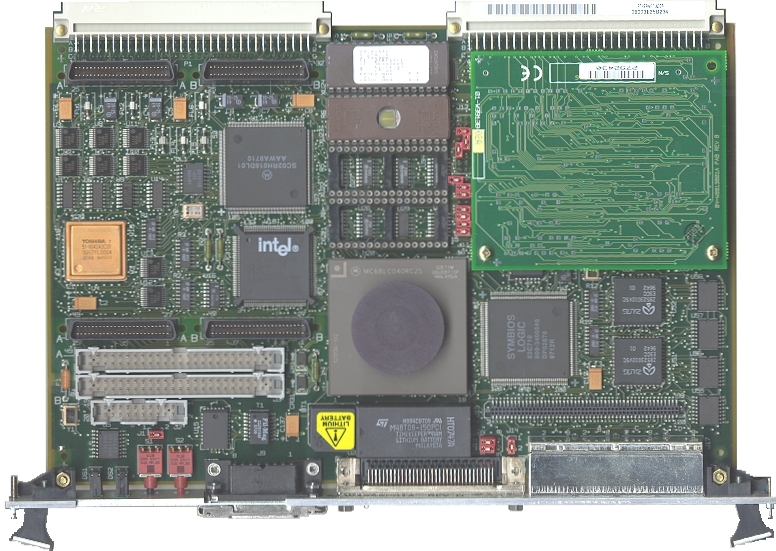

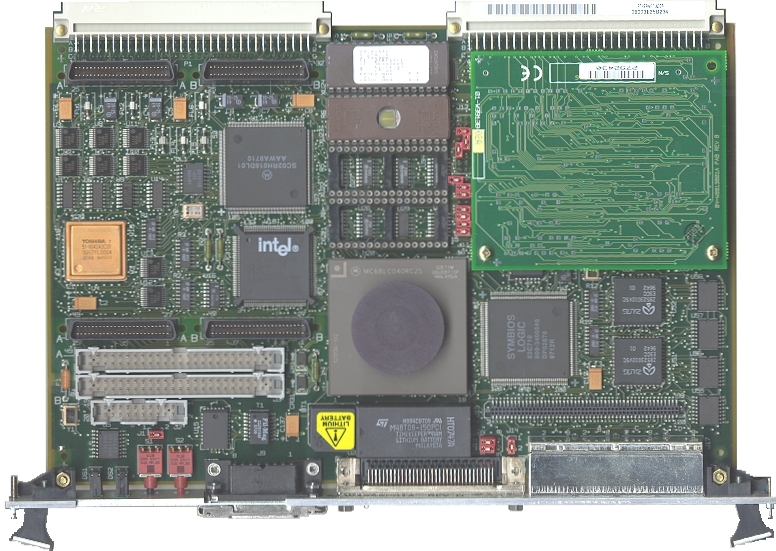

3 cartes MVME 162LX-263 = 25 Mhz MC68040

16 MB ECC SCSI/Ethernet

1 carte MVME 162LX-253 = 25 Mhz MC68LC040 16 MB ECC

SCSI/Ethernet

8 cartes MVME 162LX-213 = 25 Mhz MC68LC040 4 MB Parity

SCSI/Ethernet

- un MC68LC040 cadencé à 25 MHz microprocesseur 32 bits

avec 8Kb de cache et une unite

de gestion de la memoire MMU (le MC68LC040 est une version (( low cost

)) du MC68040 : il n'a pas

d'unité de calculs flottants FPU);

- 4 Moctects ou 16 Moctets de mémoire dynamique ;

- 1 Moctets de mémoire FLASH ;

- 128 Kbytes de mémoire statique sauvegardée par une battery ;

- 8 Kbytes de mémoire non volatile pour le calandrier et horloge : le TIMEKEEPER M48T08 ;

- 4 supports de 32 broches pour la PROMs, 2 supports sont occupés

:

l'un contient le chargeur/debugger 162Bug Motorala,

l'autre le XRAY debugger de MicroTec ;

- deux contr^oleurs pour 4 lignes synchrone/asynchrone : deux Zilog Z85230 ;

- un contr^oleur ETHERNET : l'Intel 82596CA ;

- un contr^oleur SCSI : le NCA 53C710 ;

- un contr^oleur mémoire (le MCChip un asic), qui entre autres

fonctions, offre :

+ 4 timers 32bits programmables ; + la gestion des interruptions

des contr^oleurs

d'entrées/sorties.

- contr^oleur de bus VME Maitre/Esclave jusqu'a 64 bits de donnees et

32 lignes d'adresses : (le VMEchip2 un asic).

Le Z85230 comporte deux canaux: le canal A et le canal B. Chaque canal

comporte deux registres qui sont "mapp'es" par le MCchip

dans l'espace

d'adressage de la carte: il s'agit des registres Port Control Register

et Port Data Register.

Les adresses sont les suivantes :

Premier contr^oleur

| Port Control Register Port Data Register | |

|

canal A

canal B |

FFF45005

FFF45007

FFF45001 FFF45003 |

| Port Control Register Port Data Register | |

|

canal A

canal B |

FFF45805

FFF45807

FFF45801 FFF45803 |

|

|

|

|

|

|

|||

|

|

|

|

|

Base Register |

|||

|

|

|

||||||

|

|

|

||||||

|

|

|

||||||

|

|

|

||||||

|

|

Count Register |

Clock Adjust |

Control |

Control |

|||

|

|

Interrupt Control |

Interrupt Control |

Interrupt Control |

Interrupt Control |

|||

|

|

Error Interrupt Control |

Control |

Control |

Control |

|||

|

|

Register |

Register |

|

|

|||

|

|

Size |

Options |

Size |

|

|||

|

|

Status |

|

Interrupt Control |

Interrupt Control |

|||

|

|

Status |

Inputs |

Version |

Control |

|||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|||

|

|

|

||||||

|

|

|

Time Control |

Time Control |

Interrupt Control |

|||

|

|

|

|

Watchdog |

|

|||

|

|

DRAM Control |

(reserved) |

Select MPU Status |

|

|||

|

|

|

||||||

Registre ID et le registre de Revision

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FAST Bit de contr^ole de la vitesse pour m'emoire BBRAM. Ne jamais modifier de bit !

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ce registre est utilise pour envoyer un numero de vecteur vers le MC68xx040 pendant les cycles de reconnaissance d'interruption. Seul les bits 7 'a 4 sont modifiables. Les 4 autres bits sont utilises pour encoder l'origine de l'interruption comme le montre le tableau suivant:

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Programmer les Timers

Le MCchip possede 4 timers programmables.Les registres Tick Timer Counter

Ce sont des registres de 32 bits qui sont incr'ement'es chaque fois qu'apparait un Tick d'horloge si le timer correspondent est active'.

Les operations permises sont la lecture et l'ecriture. Un RESET ne modifie pas les bits de ces registres. Quand vous programmez un timer

pour g'en'erer une interruption p'eriodique, le Tick Timer Counter devra etre mis 'a zero par logiciel. Sinon l'apparition de la premiere

interruption ne serra pas determin'ee: soit au plus-tard dans 71,6 minutes !Les registres Tick Compare

Ce sont des registres de 32 bits. les operations permises sont la lecture et l'ecriture. Un RESET remet a zero les bits de ces registres.

La valeur du Tick Timer Counter est compare au Tick Compare. Lorsqu'ils sont egaux, une interruption est envoyer vers le bus local

et le counter d'overflow est incremente. Si le mode clear on compare est valide, le Tick Timer Counter est remis 'a zero.Le Registre Prescaler Clock Adjust Register

Ce registre de 8 bits permet de programmer la frequence d'apparition des Ticks des 4 timers suivant l'equation suivante:Tick clock MHz = processor clock MHz / (256 - precaler value)

Remarque: la valeur $FF n'est pas permise, la fr'equence maximum pour les Ticks timers est donc la fr'equences du processeur divise par deux.

Par exemple si l'on veut un Tick `a 1 MHz, l'equation devient:Prescaler value = 256 - (processor clock / Tick Clock)

Prescaler value = 256 - 25MHz

Prescaler value = $E7

Les registres de contr^ole des timers

Chaque timer a un registre de contr^ole:

|

OV3 |

OVF2 |

OVF1 |

OVF0 |

|

COVF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CEN quand ce bit vaut 1, le registre de comptage est incr'ement'e tous les Ticks (le timer fonctionne); quand ce bit vaut 0, le registre de

comptage n'est pas incr'ement'e (le timer est arr'et'e).

COC quand ce bit vaut 1, le registre de comtage est remis a z'ero quand il atteint la valeur du registre de comparaison ; si ce bit vaut 0,

le registre de comtage continue 'a ^etre incr'ement'e apre`es avoir atteint la valeur du registre de comparaison.

COVF le compteur d'overflow est remis a 0 chaque fois que l'on e'crit un 1 dans ce bit.

OVFL Ces bits constituent le compteur d'overflow. Il est incr'ement'e chaque fois ou le timer g'en'ere une interruption.Les registre de contr^ole d'interruption des Timers

|

|

|

|

IEN |

ICLR |

IL2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IL2 - IL0 Ces 3 bits code le niveau d'interruption compatible avec la famille 680000. Le niveau 0 ne g'en'ere pas d'interruption.

ICLR Ecrire un 1 dans ce bit met 'a 0 le bit INT.

IEN La mise 'a 1 de ce bit, valide les interruptions. Sa mise a 0 invalide les interruptions.

INT Quand ce bit vaut 1, c'est qu'une interruption 'a ete g'en'er'e. Ce bit passe 'a 0 en ecrivant un 1 dans le bit ICLR.

Le VMEchip2

Le VMEchip2 est un ASIC qui permet d'interfacer le bus interne de la carte MVME162LX avec le bus externe VME. Donc de pouvoir communiquer avec toutes autres cartes presentes sur le bus VME du rack. Il possede 36 registres de 32 bits: pffff bonsoir la programmation ! Heureusement nous

allons utiliser un cas particulier et simple de sa programmation (ouf !). Le chapitre 2 du manuel MVME162 Embedded Controller Programmer's Guide d''etaille les moindres bits de ce circuit.

Nous allons donc aborder le cas de figure des TP IMIPRO. Il s'agit de communiquer (lire/ecrire) via le VMEbus entre une carte maitre MVME162lx et une carte exclave d'entree/sortie (qui permet le controle/commande des robots Fischers):