CTMRM/D

MOTOROLA

# **CONFIGURABLE TIMER MODULE**

REFERENCE MANUAL

| 1  | FUNCTIONAL OVERVIEW                      |

|----|------------------------------------------|

| 2  | BUS INTERFACE UNIT SUBMODULE (BIUSM)     |

| 3  | INTERRUPTS                               |

| 4  | COUNTER PRESCALER SUBMODULE (CPSM)       |

| 5  | FREE-RUNNING COUNTER SUBMODULE (FCSM)    |

| 6  | MODULUS COUNTER SUBMODULE (MCSM)         |

| 7  | SINGLE ACTION SUBMODULE (SASM)           |

| 8  | DOUBLE ACTION SUBMODULE (DASM)           |

| 9  | PULSE WIDTH MODULATION SUBMODULE (PWMSM) |

| 10 | ELECTRICAL SPECIFICATIONS                |

| Α  | REGISTER SUMMARY                         |

| B  | CTM EXAMPLE – CTM2                       |

| С  | GLOSSARY                                 |

| D  | INDEX                                    |

|    |                                          |

| 1  | FUNCTIONAL OVERVIEW                      |

|----|------------------------------------------|

| 2  | BUS INTERFACE UNIT SUBMODULE (BIUSM)     |

| 3  | INTERRUPTS                               |

| 4  | COUNTER PRESCALER SUBMODULE (CPSM)       |

| 5  | FREE-RUNNING COUNTER SUBMODULE (FCSM)    |

| 6  | MODULUS COUNTER SUBMODULE (MCSM)         |

| 7  | SINGLE ACTION SUBMODULE (SASM)           |

| 8  | DOUBLE ACTION SUBMODULE (DASM)           |

| 9  | PULSE WIDTH MODULATION SUBMODULE (PWMSM) |

| 10 | ELECTRICAL SPECIFICATIONS                |

| Α  | REGISTER SUMMARY                         |

| Β  | CTM EXAMPLE – CTM2                       |

| С  | GLOSSARY                                 |

| D  | INDEX                                    |

|    |                                          |

# СТМ

# Configurable Timer Module Reference Manual

All Trade Marks recognized. This document contains information on new products. Specifications and information herein are subject to change without notice.

All products are sold on Motorola's Terms & Conditions of Supply. In ordering a product covered by this document the Customer agrees to be bound by those Terms & Conditions and nothing contained in this document constitutes or forms part of a contract (with the exception of the contents of this Notice). A copy of Motorola's Terms & Conditions of Supply is available on request.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

The Customer should ensure that it has the most up to date version of the document by contacting its local Motorola office. This document supersedes any earlier documentation relating to the products referred to herein. The information contained in this document is current at the date of publication. It may subsequently be updated, revised or withdrawn.

# **Conventions**

Where abbreviations are used in the text, an explanation can be found in the glossary, at the back of this document. Register and bit mnemonics are defined in the paragraphs describing them.

A horizontal bar over a signal name indicates that the signal is active-low, e.g. RESET.

Unless stated otherwise, shaded cells in a register diagram indicate that the bits are either unimplemented bits or reserved, and always read as zero.

In register diagrams, 'u' indicates that the state on reset is undefined.

When a bit is 'set', it has the value 1 (one).

When a bit is 'clear', it has the value 0 (zero).

When a bit is 'reset', it has its default value, which may be 1 or 0.

# **Reference documents**

CPU16 Central Processor Unit Reference Manual (CPU16RM/D) CPU32 Central Processor Unit Reference Manual (CPU32RM/AD) GPT General Purpose Timer Reference Manual (GPTRM/AD) An introduction to the HC16 for HC11 users (AN461/D) - Cut along this line to remove -

#### CUSTOMER FEEDBACK QUESTIONNAIRE (CTMRM)

Motorola wishes to continue to improve the quality of its documentation. We would welcome your feedback on the publication you have just received. Having used the document, please complete this card (or a photocopy of it, if you prefer).

1. How would you rate the quality of the document? Check one box in each category.

|    | Organization<br>Readability<br>Understandabi<br>Accuracy<br>Illustrations<br>Comments: | Excellent                                          | Poor                                     | Tables<br>Table of contents<br>Index<br>Page size/binding<br>Overall impression | Excellent                              |   | or<br>]<br>]<br>]<br>]      |

|----|----------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------|---|-----------------------------|

| 2. |                                                                                        | vice for new application                           | _                                        | han one option applies, p<br>Other Pleas<br>                                    | blease rank them (                     | , |                             |

| 3. | How well does                                                                          | this manual enable yo<br>Completely                | ou to perform the ta<br>Not at all       | ask(s) outlined in questio<br>Comments:                                         | n 2?                                   |   |                             |

| 4. | How easy is it t                                                                       | to find the information<br>Easy                    | you are looking fo<br>Difficult          | Comments:                                                                       |                                        |   |                             |

| 5. |                                                                                        | echnical detail in the f                           | J. J | sufficient to allow you to u                                                    | understand how th<br>Too little detail |   | nctions?<br>Too much detail |

|    | SECTION 1<br>SECTION 2<br>SECTION 3                                                    | FUNCTIONAL OVER<br>BUS INTERFACE U<br>INTERRUPTS   | NIT SUBMODULE                            |                                                                                 |                                        |   |                             |

|    | SECTION 4<br>SECTION 5<br>SECTION 6                                                    | COUNTER PRESCA<br>FREE-RUNNING CO<br>MODULUS COUNT | OUNTER SUBMOI                            | DULE (FCSM)                                                                     |                                        |   |                             |

|    | SECTION 7<br>SECTION 8                                                                 | SINGLE ACTION SU<br>DOUBLE ACTION S                | JBMODULE (SAS                            | M)                                                                              |                                        |   |                             |

|    | SECTION 9                                                                              | PULSE WIDTH MOD                                    |                                          | ,                                                                               |                                        |   |                             |

|    | SECTION 10                                                                             | ELECTRICAL SPEC                                    |                                          |                                                                                 |                                        |   |                             |

|    |                                                                                        | CTM EXAMPLE – C                                    |                                          |                                                                                 |                                        |   |                             |

|    | APPENDIX C<br>APPENDIX D                                                               |                                                    |                                          |                                                                                 |                                        |   |                             |

| 6. | Comments: _<br>Have you found                                                          | d any errors? If so, ple                           | ase comment:                             |                                                                                 |                                        |   |                             |

| 7. | From your poin                                                                         | t of view, is anything r                           | missing from the d                       | ocument? If so, please sa                                                       | ay what:                               |   |                             |

11/Nov/97@15:52

\_ \_ \_

. \_ \_ \_

-this line does not form part of the document-

1

1

| 8.  | How could we improve this document?                                                                                |                                                                                                                                  |                                   |

|-----|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|     |                                                                                                                    |                                                                                                                                  |                                   |

| 9.  | How would you rate Motorola's documentation?                                                                       |                                                                                                                                  | 1                                 |

|     | Excellent     In general     Against other semiconductor suppliers                                                 | Poor                                                                                                                             |                                   |

| 10. | Which semiconductor manufacturer provides the best                                                                 | technical documentation?                                                                                                         | 1                                 |

| 11. | Which company (in any field) provides the best technic                                                             | cal documentation?                                                                                                               |                                   |

| 12. | How many years have you worked with microprocesso                                                                  | ors?                                                                                                                             | 1                                 |

|     | Less than 1 year 1-3 years 3-5 years                                                                               | Ars More than 5 years                                                                                                            | 1                                 |

|     | Sec                                                                                                                | cond fold back along this line –                                                                                                 | <br> <br>                         |

|     | By air mail<br>Par avion<br>BRS NUMBER PHQ-B/207/G<br>CCRI NUMERO PHQ-B/207/G                                      | NE PAS AFFRANCHIR<br>NO STAMP REQUIRED                                                                                           | Fik                               |

|     | SECTION                                                                                                            | REPONSE PAYEE<br>GRANDE-BRETAGNE<br>Motorola Ltd.,<br>Colvilles Road,<br>Kelvin Industrial Estate,<br>EAST KILBRIDE,<br>G75 8BR. | First fold back along this line – |

|     | $(\mathbf{A})$                                                                                                     | GREAT BRITAIN.                                                                                                                   |                                   |

|     | MOTOROLA LTD.<br>Semiconductor Products Sector                                                                     | F.A.O. Technical Publications Manager (re: CTMRM/D)                                                                              |                                   |

|     | – – – – – – – – – – – – – – – – – – –                                                                              | hird fold back along this line –                                                                                                 | <br>+                             |

| 13. | Currently there is some discussion in the semiconducto<br>form. If you have any opinion on this subject, please of | or industry regarding a move towards providing data sheets in el<br>omment.                                                      | lectronic                         |

| 14. | We would be grateful if you would supply the following                                                             | information (at your discretion), or attach your card.                                                                           |                                   |

|     | Name:                                                                                                              | Phone No:                                                                                                                        |                                   |

|     | Position:                                                                                                          | FAX No:                                                                                                                          | 1                                 |

|     | Department:                                                                                                        |                                                                                                                                  | 1                                 |

|     | Company:                                                                                                           |                                                                                                                                  |                                   |

|     | Address:                                                                                                           |                                                                                                                                  |                                   |

|     | Thank you for helping us improve our documentation,<br>Graham Livey, Technical Publications Manager, Motor         | rola Ltd., Scotland.                                                                                                             |                                   |

# TABLE OF CONTENTS

Paragraph Number

Title

Page Number

#### 1 FUNCTIONAL OVERVIEW

| CTM features                           | .1-1                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTM description                        | .1-2                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Byte/word/long word accesses           | .1-3                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8-bit (byte) accesses                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 16-bit (word) aligned accesses         | .1-4                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 16-bit (word) misaligned accesses      | .1-4                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 32-bit (long word) aligned accesses    |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 32-bit (long word) misaligned accesses | .1-5                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3-byte accesses                        | .1-5                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| The time base bus system               | .1-5                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Pin descriptions                       | .1-6                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Input capture (IC) concepts            | .1-6                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Output compare (OC) concepts           | .1-7                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Pulse accumulator (PA) concepts        |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Pulse width modulation (PWM) concepts  | .1-9                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Using and clearing flag bits           | .1-10                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                        | CTM description<br>Byte/word/long word accesses<br>8-bit (byte) accesses<br>16-bit (word) aligned accesses<br>16-bit (word) misaligned accesses<br>32-bit (long word) aligned accesses<br>32-bit (long word) misaligned accesses<br>3-byte accesses<br>The time base bus system<br>Pin descriptions<br>Input capture (IC) concepts<br>Output compare (OC) concepts<br>Pulse accumulator (PA) concepts<br>Pulse width modulation (PWM) concepts |

#### 2 BUS INTERFACE UNIT SUBMODULE (BIUSM)

| 2.1   | BIUSM description                           | 2-1 |

|-------|---------------------------------------------|-----|

|       | Freeze action on the BIUSM                  |     |

| 2.3   | LPSTOP action on the BIUSM                  | 2-1 |

| 2.4   | STOP and WAIT action on the BIUSM           | 2-2 |

| 2.5   | BIUSM registers                             | 2-2 |

| 2.5.1 |                                             |     |

| 2.5.2 | BIUTEST — BIUSM test configuration register | 2-4 |

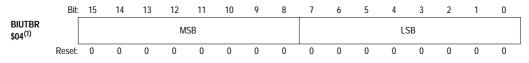

| 2.5.3 | BIUTBR — BIUSM time base register           | 2-5 |

3

# INTERRUPTS

| 3.1 | Interrupt levels on the IMB | 3-1 |

|-----|-----------------------------|-----|

|     | Arbitration                 |     |

| 3.3 | CTM daisy-chain priority    | 3-2 |

#### 4 COUNTER PRESCALER SUBMODULE (CPSM)

| 4.1 | CPSM description             | 4-1 |

|-----|------------------------------|-----|

|     | Freeze action on the CPSM    |     |

|     | CPSM registers               |     |

|     | CPCR — CPSM control register |     |

|     | CPTR — CPSM test register    |     |

#### 5

#### FREE-RUNNING COUNTER SUBMODULE (FCSM)

| 5.1   | FCSM description                                 | 5-1 |

|-------|--------------------------------------------------|-----|

|       | The FCSM counter                                 |     |

| 5.3   | FCSM clock sources                               | 5-2 |

| 5.3.1 | FCSM external event counting                     | 5-2 |

| 5.4   | The FCSM time base bus driver                    | 5-3 |

| 5.5   | FCSM interrupts                                  | 5-3 |

|       | Freeze action on the FCSM                        |     |

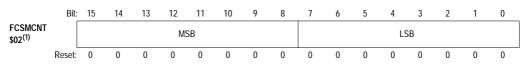

| 5.7.1 | FCSMSIC — FCSM status/interrupt/control register | 5-4 |

|       | FCSMCNT — FCSM counter register                  |     |

#### 6 MODULUS COUNTER SUBMODULE (MCSM)

| 6.1    | MCSM description                           | 6-1 |

|--------|--------------------------------------------|-----|

|        | The MCSM modulus latch                     |     |

| 6.3    | The MCSM counter                           | 6-2 |

| 6.3.1  | Loading the MCSM counter register          | 6-2 |

| 6.3.1. | 1 Using the MCSM as a free-running counter | 6-3 |

| 6.4    | MCSM clock sources                         | 6-3 |

| 6.4.1  | MCSM external event counting               | 6-3 |

| 6.5    | The MCSM time base bus driver              | 6-4 |

| Paragraph |  |

|-----------|--|

| Number    |  |

| 6.6   | MCSM interrupts                      | .6-4 |

|-------|--------------------------------------|------|

|       | Freeze action on the MCSM            |      |

|       | MCSM registers                       |      |

| 6.8.1 |                                      |      |

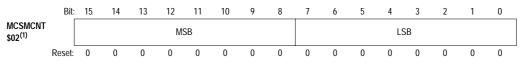

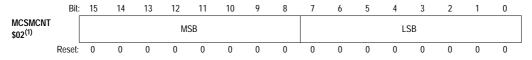

| 6.8.2 | MCSMCNT — MCSM counter register      | .6-7 |

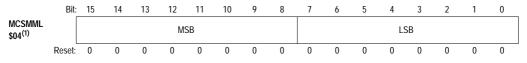

| 6.8.3 | MCSMML — MCSM modulus latch register | .6-8 |

#### 7 SINGLE ACTION SUBMODULE (SASM)

| SASM description                                | 7-1                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SASM modes of operation                         | 7-2                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Input capture (IC) mode                         | 7-4                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output compare (OC) mode                        | 7-4                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output compare and toggle (OCT) mode            | 7-5                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Output port (OP) mode                           | 7-5                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Freeze action on the SASM                       | 7-6                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SASM registers                                  | 7-6                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SICA — SASM status/interrupt/control register A | 7-7                                                                                                                                                                                                                                                                                                                                                                                                                                             |

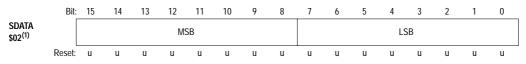

| SDATA — SASM data register A                    | 7-10                                                                                                                                                                                                                                                                                                                                                                                                                                            |

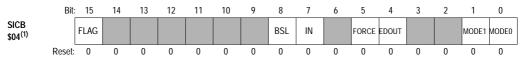

| SICB — SASM status/interrupt/control register B | 7-10                                                                                                                                                                                                                                                                                                                                                                                                                                            |

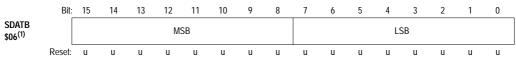

| SDATB — SASM data register B                    | 7-11                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                 | SASM description<br>SASM modes of operation<br>Clearing and using the FLAG bits<br>Input capture (IC) mode<br>Output compare (OC) mode<br>Output compare and toggle (OCT) mode<br>Output port (OP) mode<br>SASM interrupts<br>Freeze action on the SASM<br>SASM registers<br>SICA — SASM status/interrupt/control register A<br>SDATA — SASM data register A<br>SICB — SASM status/interrupt/control register B<br>SDATB — SASM data register B |

#### 8 DOUBLE ACTION SUBMODULE (DASM)

| 8.1     | DASM description                          | 8-2  |

|---------|-------------------------------------------|------|

| 8.2     | 32-bit coherent access                    | 8-3  |

| 8.3     | DASM modes of operation                   | 8-3  |

| 8.3.1   | Disable (DIS) mode                        | 8-4  |

| 8.3.2   | Input pulse width measurement (IPWM) mode | 8-4  |

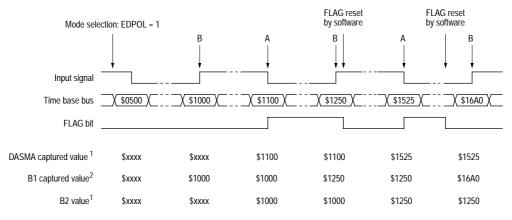

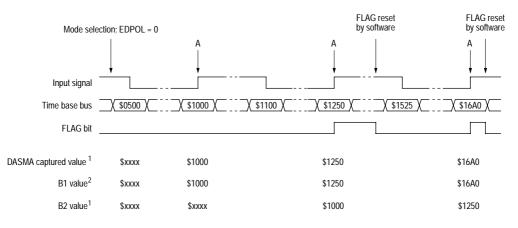

| 8.3.3   | Input period measurement (IPM) mode       | 8-5  |

| 8.3.4   | Input capture (IC) mode                   | 8-7  |

| 8.3.5   | Output compare (OCB and OCAB) modes       | 8-7  |

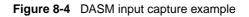

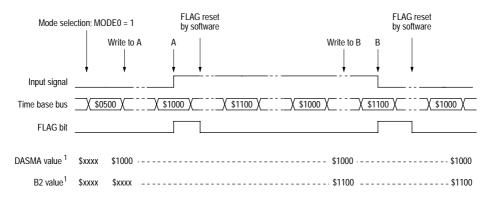

| 8.3.5.1 | Single shot output pulse operation        | 8-8  |

| 8.3.5.2 | Single output compare operation           | 8-9  |

| 8.3.5.3 | Output port bit operation                 | 8-9  |

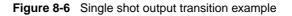

| 8.3.6   | Output pulse width modulation (OPWM) mode | 8-10 |

| 8.4     | DASM interrupts                           | 8-12 |

| 8.5     | Freeze action on the DASM                 |      |

| Paragrap<br>Number | h<br>Title                                       | Page<br>Number |

|--------------------|--------------------------------------------------|----------------|

|                    |                                                  |                |

| 8.6                | DASM registers                                   | 8-13           |

| 8.6.1              | DASMSIC — DASM status/interrupt/control register | 8-14           |

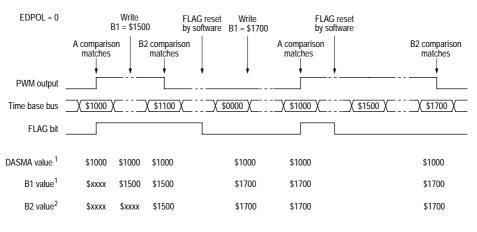

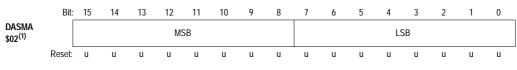

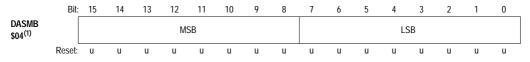

| 8.6.2              | DASMA — DASM data register A                     | 8-18           |

| 8.6.3              | DASMB — DASM data register B                     |                |

| 8.7                | DASM examples                                    | 8-20           |

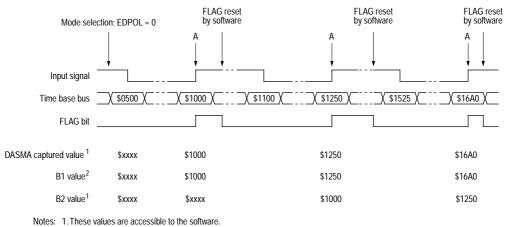

| 8.7.1              | IC mode example                                  | 8-20           |

| 8.7.2              | IPM mode example                                 | 8-21           |

| 8.7.3              | OCB mode example                                 | 8-22           |

| 8.7.4              | PWM mode example                                 | 8-24           |

|                    |                                                  |                |

#### 9 PULSE WIDTH MODULATION SUBMODULE (PWMSM)

| 9.1     | PWMSM features                                  | 9-1  |

|---------|-------------------------------------------------|------|

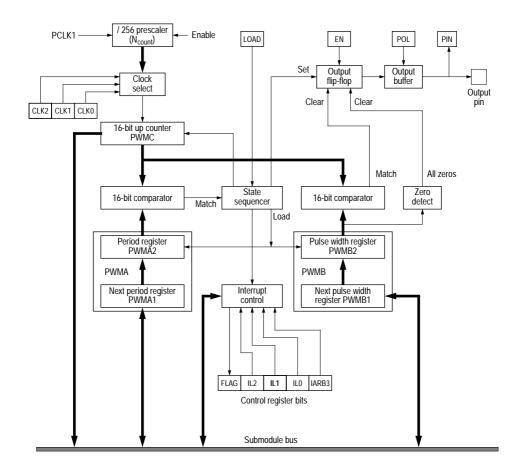

| 9.2     | PWMSM description                               | 9-2  |

| 9.2.1   | Output flip-flop and pin                        |      |

| 9.2.2   | Clock selection                                 | 9-2  |

| 9.2.3   | The PWMSM counter (PWMC)                        | 9-3  |

| 9.2.4   | PWMSM period registers and comparator           | 9-4  |

| 9.2.5   | PWMSM pulse width registers and comparator      | 9-4  |

| 9.2.5.1 | 1 0% and 100% 'pulses'                          | 9-5  |

| 9.2.6   | PWMSM coherency                                 |      |

| 9.2.7   | PWMSM interrupts                                | 9-6  |

| 9.2.8   | Freeze action on the PWMSM                      |      |

| 9.3     | PWM frequency, pulse width and resolution       | 9-6  |

| 9.3.1   | PWM frequency                                   |      |

| 9.3.2   | PWM pulse width                                 |      |

| 9.3.3   | PWM period and pulse width register values      | 9-8  |

| 9.4     | PWMSM register map and registers                | 9-9  |

| 9.4.1   | PWMSIC — Status, interrupt and control register | 9-9  |

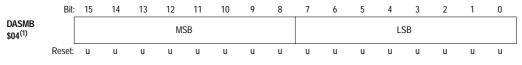

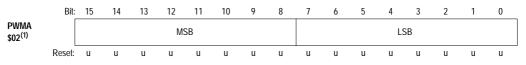

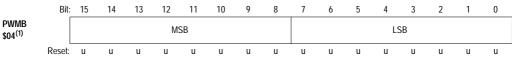

| 9.4.2   | PWMA — PWM period register                      | 9-12 |

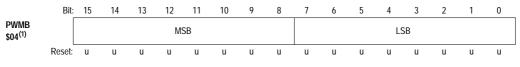

| 9.4.3   | PWMB — PWM pulse width register                 |      |

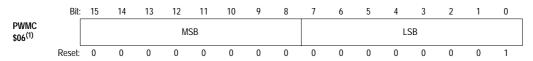

| 9.4.4   | PWMC — PWM counter register                     | 9-14 |

|         |                                                 |      |

#### 10

## **ELECTRICAL SPECIFICATIONS**

| 10.1 | FCSM and MCSM timing information | 10-1 |

|------|----------------------------------|------|

| 10.2 | SASM timing information          | 10-6 |

| 10.3 | DASM timing information          |      |

|      | PWMSM timing information         |      |

#### APPENDIX A REGISTER AND BIT SUMMARY

| A.1 BIU | SM registers and bits                                 | A-1  |

|---------|-------------------------------------------------------|------|

| A.1.1   | BIUMCR — BIUSM module configuration register          | A-1  |

| A.1.1.1 | STOP — Stop enable                                    | A-1  |

| A.1.1.2 | FRZ — Freeze enable                                   | A-1  |

| A.1.1.3 | VECT7, VECT6 — Interrupt vector base number bits      | A-2  |

| A.1.1.4 | IARB[2:0] — Interrupt arbitration identification bits | A-2  |

| A.1.1.5 | TBRS1, TBRS0 — Time base register bus select bits     | A-2  |

| A.1.2   | BIUTEST — BIUSM test configuration register           | A-2  |

| A.1.3   | BIUTBR — BIUSM time base register                     | A-2  |

| A.2 CP  | SM registers and bits                                 | A-3  |

| A.2.1   | CPCR — CPSM control register                          | A-3  |

| A.2.1.1 | PRUN — Prescaler running bit                          | A-3  |

| A.2.1.2 | DIV23 — Divide by 2 or divide by 3 bit                | A-3  |

| A.2.1.3 | PSEL1, PSEL0 — Prescaler division ratio select bits   | A-3  |

| A.2.2   | CPTR — CPSM test register                             |      |

| A.3 FC  | SM registers and bits                                 | A-4  |

| A.3.1   | FCSMSIC — FCSM status/interrupt/control register      | A-4  |

| A.3.1.1 | COF — Counter overflow flag bit                       | A-4  |

| A.3.1.2 | IL[2:0] — Interrupt level bits                        | A-4  |

| A.3.1.3 | IARB3 — Interrupt arbitration bit 3                   | A-4  |

| A.3.1.4 | DRVA, DRVB — Drive time base bus bits                 | A-5  |

| A.3.1.5 | IN — Input pin status bit                             | A-5  |

| A.3.1.6 | CLK[2:0] — Counter clock select bits                  | A-5  |

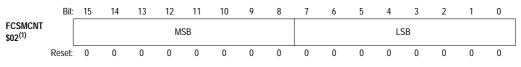

| A.3.2   | FCSMCNT — FCSM counter register                       | A-5  |

| A.4 MC  | SM registers and bits                                 | A-6  |

| A.4.1   | MCSMSIC — MCSM status/interrupt/control register      | A-6  |

| A.4.1.1 | COF — Counter overflow flag bit                       | A-6  |

| A.4.1.2 | IL[2:0] — Interrupt level bits                        | A-6  |

| A.4.1.3 | IARB3 — Interrupt arbitration bit 3                   |      |

| A.4.1.4 | DRVA, DRVB — Drive time base bus bits                 | A-7  |

| A.4.1.5 | IN2 — Clock input pin status bit                      | A-7  |

| A.4.1.6 | IN1 — Modulus load input pin status bit               |      |

| A.4.1.7 | EDGEN, EDGEP — Modulus load edge sensitivity bits     | A-7  |

| A.4.1.8 | CLK[2:0] — Counter clock select bits                  | A-7  |

| A.4.2   | MCSMCNT — MCSM counter register                       | A-8  |

| A.4.3   | MCSMML — MCSM modulus latch register                  | A-8  |

| A.5 SAS | SM registers and bits                                 |      |

| A.5.1   | SICA — SASM status/interrupt/control register A       | A-9  |

| A.5.1.1 | FLAG — Event flag bit                                 | A-9  |

| A.5.1.2 | IL[2:0] — Interrupt level bits                        |      |

| A.5.1.3 | IARB3 — Interrupt arbitration bit 3                   |      |

| A.5.1.4 | IEN — Interrupt enable bit                            |      |

| A.5.1.5 | BSL — Time base bus select bit                        | A-10 |

| Paragraph | ۱ |

|-----------|---|

| Number    |   |

| A.5.1.6 IN — Input pin status bit A-10                               |

|----------------------------------------------------------------------|

| A.5.1.7 FORCE — Force compare control bit A-10                       |

| A.5.1.8 EDOUT — Edge detect and output level bit A-10                |

| A.5.1.9 MODE1, MODE0 — SASM operating mode select bits A-10          |

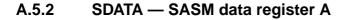

| A.5.2 SDATA — SASM data register A A-11                              |

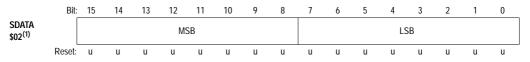

| A.5.3 SICB — SASM status/interrupt/control register B A-11           |

| A.5.3.1 FLAG — Event flag bit A-11                                   |

| A.5.3.2 BSL — Time base bus select bit A-11                          |

| A.5.3.3 IN — Input pin status bit A-11                               |

| A.5.3.4 FORCE — Force compare control bit A-12                       |

| A.5.3.5 EDOUT — Edge detect and output level bit A-12                |

| A.5.3.6 MODE1, MODE0 — SASM operating mode select bits A-12          |

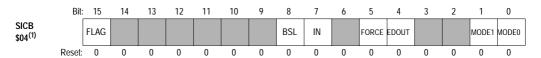

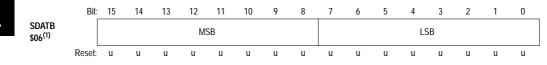

| A.5.4 SDATB — SASM data register B A-12                              |

| A.6 DASM registers and bits A-13                                     |

| A.6.1 DASMSIC — DASM status/interrupt/control register A-13          |

| A.6.1.1 FLAG — Flag status bit A-13                                  |

| A.6.1.2 IL[2:0] — Interrupt level bits A-13                          |

| A.6.1.3 IARB3 — Interrupt arbitration bit 3 A-13                     |

| A.6.1.4 WOR — Wired-OR bit A-13                                      |

| A.6.1.5 BSL — Bus select bit A-14                                    |

| A.6.1.6 IN — Input pin status bit A-14                               |

| A.6.1.7 FORCA — Force A bit A-14                                     |

| A.6.1.8 FORCB — Force B bit A-14                                     |

| A.6.1.9 EDPOL — Edge polarity bit A-14                               |

| A.6.1.10 MODE[3:0] — Mode select bits                                |

| A.6.2 DASMA — DASM data register A A-15                              |

| A.6.3 DASMB — DASM data register B A-16                              |

| A.7 PWMSM registers and bits A-17                                    |

| A.7.1 PWMSIC — PWMSM status, interrupt and control register A-17     |

| A.7.1.1 FLAG — Period completion status bit A-17                     |

| A.7.1.2 IL[2:0] — Interrupt level bits A-17                          |

| A.7.1.3 IARB3 — Interrupt arbitration bit 3 A-17                     |

| A.7.1.4 PIN — Output pin status bit A-17                             |

| A.7.1.5 LOAD — Period and pulse width register load control bit A-18 |

| A.7.1.6 POL — Output pin polarity control bit A-18                   |

| A.7.1.7 EN — PWMSM enable control bit A-18                           |

| A.7.1.8 CLK[2:0] — Clock rate selection bits                         |

| A.7.2 PWMA – PWM period register A-19                                |

| A.7.3 PWMB — PWM pulse width register A-19                           |

| A.7.4 PWMC — PWM counter register A-20                               |

|                                                                      |

Paragraph Number

#### APPENDIX B CTM EXAMPLE – CTM2

| B.1   | CTM2 registers                                | B-4 |

|-------|-----------------------------------------------|-----|

| B.1.1 | CTM2 bus interface unit submodule registers   | B-5 |

| B.1.2 | CTM2 counter prescaler submodule registers    | B-5 |

| B.1.3 | CTM2 free-running counter submodule registers | B-5 |

| B.1.4 | CTM2 modulus counter submodule registers      | B-5 |

| B.1.5 | CTM2 double action submodule registers        | B-6 |

#### APPENDIX C GLOSSARY

#### APPENDIX D INDEX

THIS PAGE INTENTIONALLY LEFT BLANK

# **LIST OF FIGURES**

| Figure<br>Number | Title                                                     | Page<br>Number |

|------------------|-----------------------------------------------------------|----------------|

| 1-1              | CTM architecture block diagram                            | 1-2            |

| 1-2              | 8-bit (byte) access (even addresses)                      | 1-3            |

| 1-3              | 8-bit (byte) access (odd addresses)                       | 1-4            |

| 1-4              | 16-bit (word) aligned access                              | 1-4            |

| 1-5              | Simplified block diagram of 16-bit input capture          | 1-7            |

| 1-6              | Simplified block diagram of 16-bit output compare         | 1-7            |

| 1-7              | Simplified block diagram of a typical pulse accumulator   | 1-8            |

| 1-8              | PWM example waveforms                                     | 1-9            |

| 1-9              | Simplified block diagram of a typical 16-bit PWM system   | 1-10           |

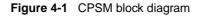

| 4-1              | CPSM block diagram                                        | 4-1            |

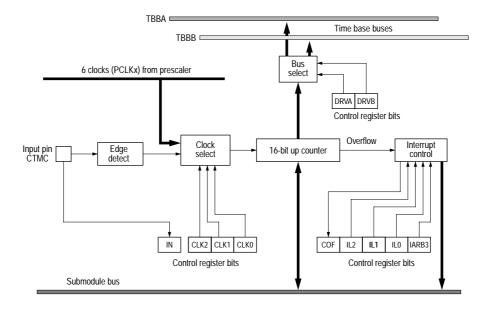

| 5-1              | FCSM block diagram                                        | 5-2            |

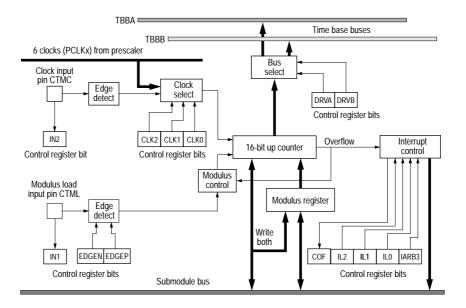

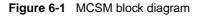

| 6-1              | MCSM block diagram                                        | 6-1            |

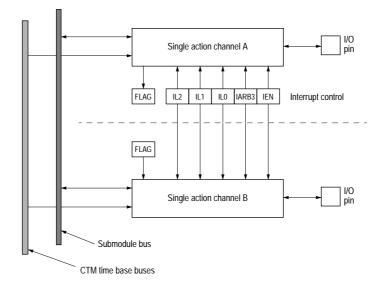

| 7-1              | SASM block diagram                                        |                |

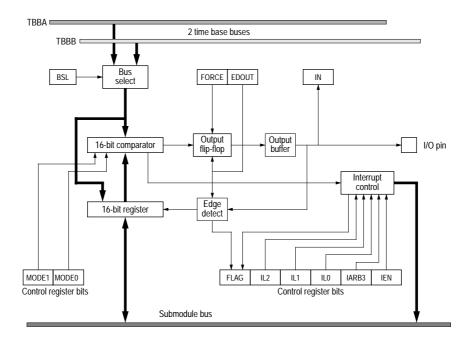

| 7-2              | SASM block diagram (channel A)                            | 7-3            |

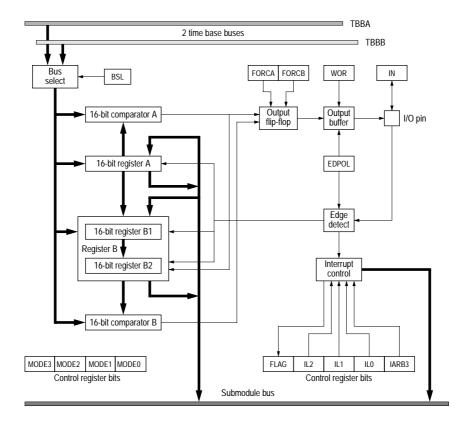

| 8-1              | DASM block diagram                                        |                |

| 8-2              | Input pulse width measurement example                     | 8-5            |

| 8-3              | Input period measurement example                          | 8-6            |

| 8-4              | DASM input capture example                                | 8-7            |

| 8-5              | Single-shot output pulse example                          | 8-9            |

| 8-6              | Single shot output transition example                     |                |

| 8-7              | DASM output pulse width modulation example                |                |

| 9-1              | Pulse width modulation submodule block diagram            |                |

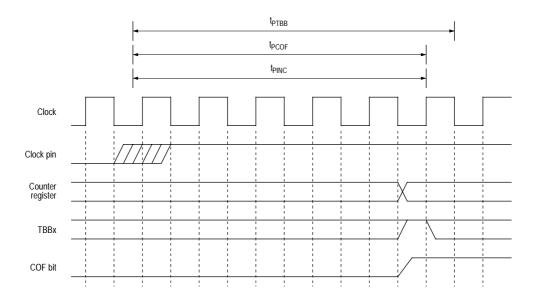

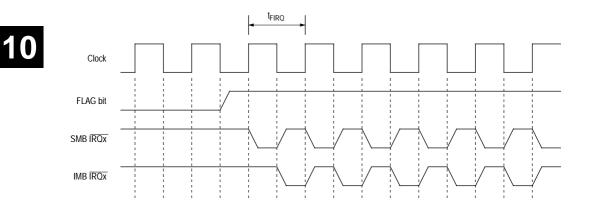

| 10-1             | FCSM and MCSM time base timing diagram example            |                |

| 10-2             | FCSM and MCSM clock pin to counter timing diagram         |                |

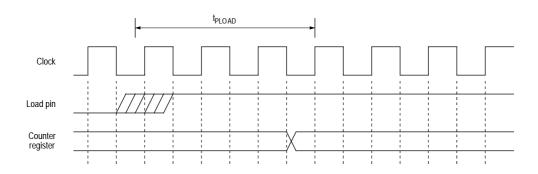

| 10-3             | MCSM load pin to counter timing diagram                   |                |

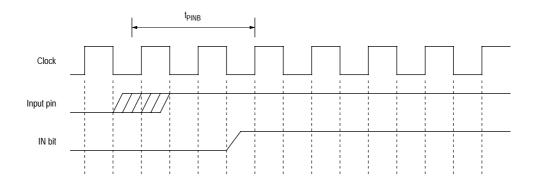

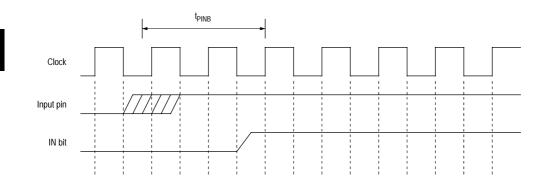

| 10-4             | FCSM and MCSM pin to IN bit timing diagram                |                |

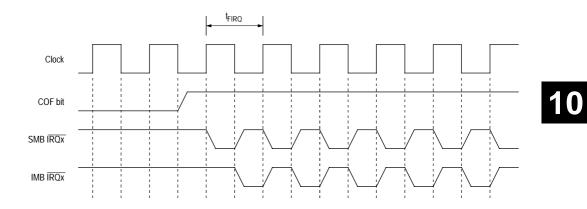

| 10-5             | FCSM and MCSM COF bit to interrupt request timing diagram |                |

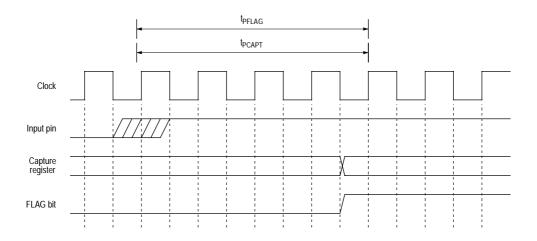

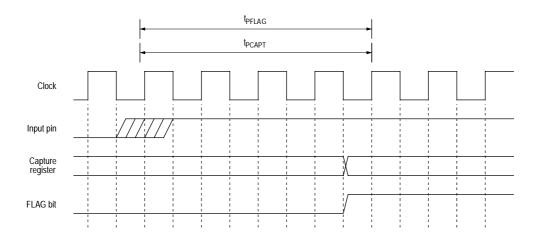

| 10-6             | SASM input capture timing diagram                         |                |

| 10-7             | SASM pin to IN bit timing diagram                         |                |

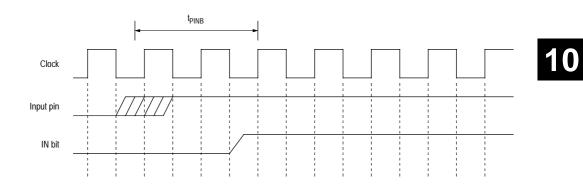

| 10-8             | SASM output compare timing diagram                        |                |

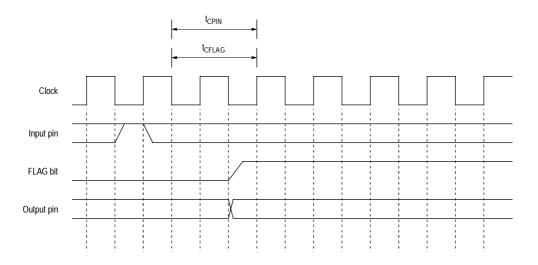

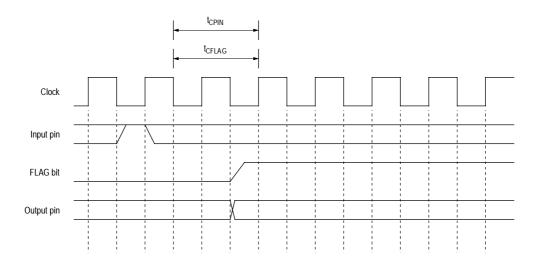

| 10-9             | SASM FLAG bit to interrupt request timing diagram         |                |

| 10-10            | DASM input capture timing diagram                         |                |

| 10-11            | DASM pin to IN bit timing diagram                         | 10-10          |

| Figure<br>Number <b>Title</b>                            | Page<br>Number |

|----------------------------------------------------------|----------------|

| 10-12 DASM output compare timing diagram                 | 10-11          |

| 10-13 DASM FLAG bit to interrupt request timing diagram  | 10-11          |

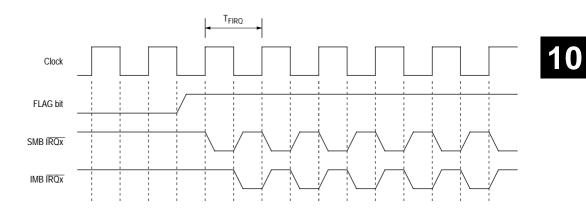

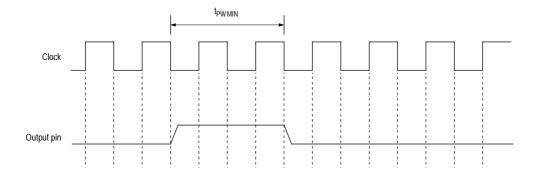

| 10-14 PWMSM minimum output pulse example timing diagram  | 10-13          |

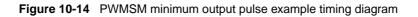

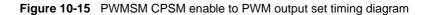

| 10-15 PWMSM CPSM enable to PWM output set timing diagram | 10-13          |

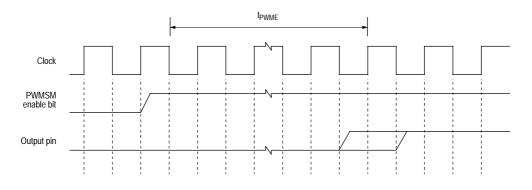

| 10-16 PWMSM enable to output set timing diagram          | 10-14          |

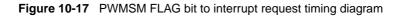

| 10-17 PWMSM FLAG bit to interrupt request timing diagram | 10-14          |

| B-1 Configurable timer module 2 (CTM2)                   | B-2            |

# LIST OF TABLES

| Number   | Title                                                                        | Number   |

|----------|------------------------------------------------------------------------------|----------|

| litambol |                                                                              | i tumboi |

| 2-1      | BIUSM register map                                                           | 2-2      |

| 3-1      | CTM submodule and interrupt vector number convention                         |          |

| 4-1      | CPSM register map                                                            | 4-2      |

| 5-1      | FCSM register map                                                            | 5-4      |

| 6-1      | MCSM register map                                                            | 6-5      |

| 7-1      | SASM register map                                                            | 7-7      |

| 8-1      | DASM modes of operation                                                      | 8-3      |

| 8-2      | DASM PWM example output frequencies/resolutions at f <sub>SYS</sub> = 16 MHz | 8-12     |

| 8-3      | DASM register map                                                            | 8-13     |

| 9-1      | PWM pulse and frequency ranges (in Hz) using /2 option (16.78 MHz)           | 9-6      |

| 9-2      | PWM pulse and frequency ranges (in Hz) using /3 option (16.78 MHz)           | 9-7      |

| 9-3      | PWMSM register map                                                           | 9-9      |

| 9-4      | PWMSM output pin polarity selection                                          | 9-11     |

| 9-5      | PWMSM clock rate selection                                                   | 9-13     |

| 10-1     | FCSM timing characteristics                                                  | 10-1     |

| 10-2     | MCSM timing characteristics                                                  | 10-2     |

| 10-3     | SASM timing characteristics                                                  |          |

| 10-4     | DASM timing characteristics                                                  | 10-9     |

| 10-5     | PWMSM timing characteristics                                                 |          |

| B-1      | Time base bus allocation                                                     |          |

| B-2      | CTM2 interrupt priority, vector allocation and pin allocation                |          |

| B-3      | CTM2 register map                                                            |          |

| B-4      | BIUSM register map                                                           |          |

| B-5      | CPSM register map                                                            | B-5      |

| B-6      | FCSM register map                                                            |          |

| B-7      | MCSM register map                                                            |          |

| B-8      | DASM register map                                                            | B-6      |

|          |                                                                              |          |

Table

Page

THIS PAGE INTENTIONALLY LEFT BLANK

# **1** FUNCTIONAL OVERVIEW

The configurable timer module (CTM) is an integral module of Motorola's family of modular microcontrollers. Members of this family are normally composed of several modules, interconnected by means of the intermodule bus (IMB). The CTM is unusual in the sense that it is, in itself, modular and is composed of submodules, making it easily configurable for different kinds of applications.

#### 1.1 CTM features

- Modular architecture

- Counter submodules:

- Clock prescaler

- 16-bit free-running counter

- 16-bit modulus counter

- Action submodules:

- Single action input capture/output compare channels

- Double action input capture/output compare channels, with PWM (pulse width modulation) mode

- PWM channels

- I/O pin for each input capture/output compare

- Output-only pin for each PWM channel

- External clock input capability

- Interrupt capability on all capture/compare/PWM channels and on counter overflow conditions

- Two, three or four time base buses, allowing great flexibility in CTM configuration

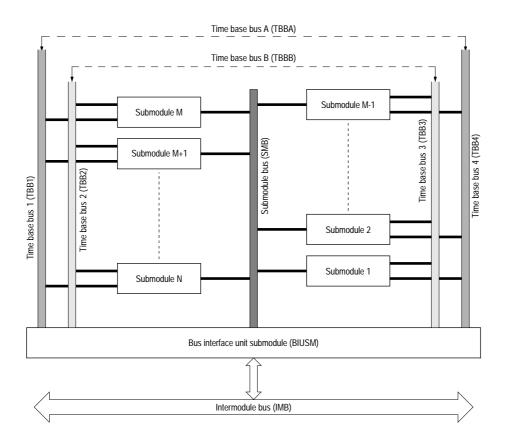

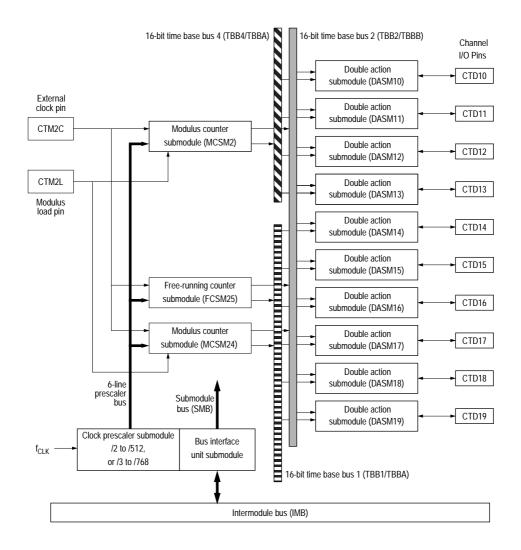

The highly modular architecture of the CTM is illustrated in Figure 1-1. Submodules are located on either side of the CTM's internal submodule bus (SMB). All data and control signals within the CTM are passed over this bus. The SMB is connected to the outside world via a special CTM submodule, known as the bus interface unit submodule (BIUSM), which is connected to the intermodule bus (IMB) and hence to the main CPU. This configuration allows the CPU to access the data and control registers in each CTM submodule on the SMB.

Figure 1-1 CTM architecture block diagram

Four local time base buses (TBB1 – TBB4) are arranged in such a way that each CTM submodule can be connected to two of them. As can be seen in Figure 1-1, CTM submodules numbered 1 to M-1 can be connected to TBB3 and TBB4 and CTM submodules M to N can be connected to TBB1 and TBB2. Control bits within each CTM submodule allow the software to connect the submodule to the desired time base bus(es). During the design of the CTM module, the four local time base

buses can be connected together (as shown by the dotted lines in Figure 1-1) to form two time base buses TBBA (TBB1/TBB4) and TBBB (TBB2/TBB3). The time base buses are each 16-bits wide and are used to transfer timing information from counters to action submodules. Each CTM submodule can either be a clock source module (and drive one or two of the time base buses) or an action submodule (and read and react to the timing information on the time base buses).

Every CTM module implementation must include at least a BIUSM and some form of clock submodule. All other submodules are optional and would be selected from a library of CTM submodules at the design stage, as required by the user to meet the needs of his application.

## 1.3 Byte/word/long word accesses

All CTM registers and data buses are 16 bits wide. Consequently, 16-bit (word) accesses are the normal case. 8-bit and 32-bit accesses are also permitted; however, as there is no pipelining in the CTM, 8-bit coherency is not supported.

## 1.3.1 8-bit (byte) accesses

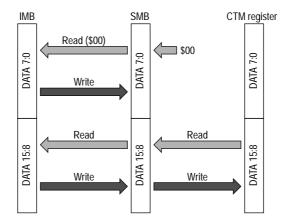

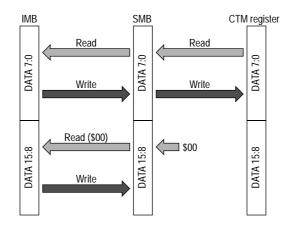

8-bit accesses are illustrated in Figure 1-2 for even addresses and Figure 1-3 for odd addresses.

Figure 1-2 8-bit (byte) access (even addresses)

## 1.3.2 16-bit (word) aligned accesses

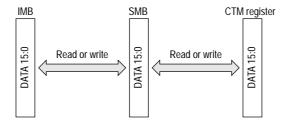

16-bit aligned access is the normal case and such accesses of counter or action submodule registers is coherent. This is illustrated in Figure 1-4.

Figure 1-3 8-bit (byte) access (odd addresses)

Figure 1-4 16-bit (word) aligned access

## 1.3.3 16-bit (word) misaligned accesses

A 16-bit misaligned access consists of two 8-bit accesses, the first to an odd address (see Figure 1-3), the second to the following even address (see Figure 1-2). A 16-bit misaligned access is treated by the BIU as an 8-bit odd address access. It is then the responsibility of the bus master to access the following byte. As in the case of the 8-bit access, since there is no pipelining, coherency is not supported.

*Note:* Neither CPU16 nor CPU32 (see section on reference documents at the beginning ot this document) support 16-bit misaligned accesses.

## 1.3.4 32-bit (long word) aligned accesses

A long word aligned access consists of two 16-bit aligned accesses (see Figure 1-4). When a long word access is attempted, a signal line is activated on the SMB during the access of the high order byte. This allows the CTM architecture to be compatible with submodules supporting long word coherency.

## 1.3.5 32-bit (long word) misaligned accesses

A long word misaligned access consists of three accesses: first a byte access to an odd address (see Figure 1-3), followed by a 16-bit aligned access to the following even address (see Figure 1-4), followed by a byte access to the remaining even address (see Figure 1-2). Note that the latter two accesses (16-bit aligned access followed by byte access to an even address) represent what is called a 3-byte access. As there is no pipelining, coherency is not supported.

*Note:* Neither CPU16 nor CPU32 support 32-bit misaligned accesses.

#### 1.3.6 3-byte accesses

A 3-byte access is normally part of a long word misaligned access. It consists of a 16-bit aligned access (see Figure 1-4), followed by a byte access to the remaining even address (see Figure 1-2). A 3-byte access is treated by the BIUSM as a 16-bit aligned access. It is then the responsibility of the bus master to access the following byte. As there is no pipelining, coherency is not supported.

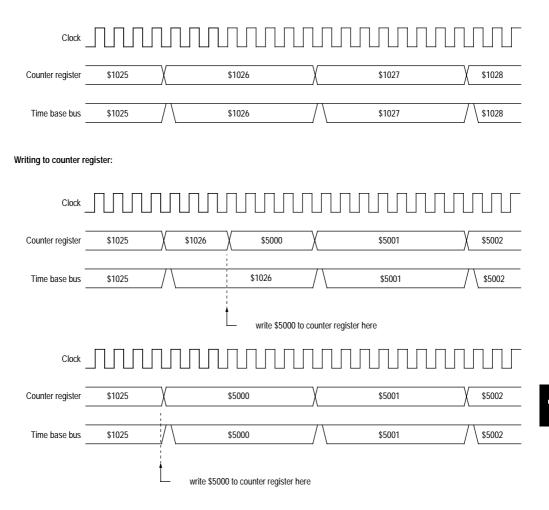

#### 1.4 The time base bus system

The time base bus system is composed of four 16-bit buses: TBB1, TBB2, TBB3 and TBB4 (see Figure 1-1). Typically, TBB2 and TBB3 are tied together to form a global bus (TBBB) while TBB1 and TBB4 remain as partial buses (collectively called TBBA).

How the submodules are connected to these time base buses is different for each CTM configuration. This is shown generically in Figure 1-1, where all counter and action submodules in the right half of the diagram (numbered from 1 to M-1) can be connected to TBB3 and/or TBB4, and all submodules in the left half of the diagram (numbered from M to N) can be connected to TBB1 and/or TBB2. An example of how the time base buses are configured and how the submodules are connected to them in a practical CTM module (CTM2) is provided in Appendix B.

The time base buses are precharge/discharge type buses with wired-OR capability, so that no hardware damage occurs when several counters are driving the same bus at the same time.

Depending on software options, counter and action submodules located in the left half of Figure 1-1 (submodules M to N) can be connected to buses TBB1 or TBB2, while counter and action submodules located in the right half of Figure 1-1 (submodules 1 to M-1) can be connected to buses TBB3 and TBB4.

#### 1.5 Pin descriptions

Input/output requirements are specific to each CTM submodule; pin allocation and functionality is described in the relevant sections of this document.

## 1.6 Input capture (IC) concepts

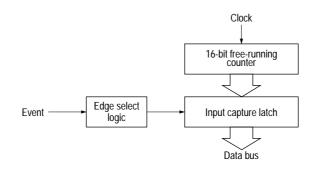

A typical 16-bit input capture function is shown in Figure 1-5. It has three basic parts: edge select logic, a 16-bit input capture latch and a 16-bit free-running counter. The edge select logic determines the input signal transition (rising or falling) that triggers the input capture circuitry. When the selected transition occurs, the contents of the counter are latched into the input capture latch. This action sets a status flag indicating that an input capture has occurred. An interrupt is generated if enabled. The value of the count latched or 'captured' is the time of the event. Because this value is stored in the input capture register when the actual event occurs, user software can respond to this event at a later time and determine the actual time of the event. However, this must be done prior to another input capture on the same pin; otherwise, the previous time value will be lost.

By recording the times for successive edges on an incoming signal, software can determine the period and/or pulse width of the signal. To measure a period, two successive edges of the same polarity are captured. To measure a pulse width, consecutive edges of opposing polarity are captured. For example, to measure the high time of a pulse, the input transition time is captured on the rising edge and subtracted from the time captured on the subsequent falling edge. When the period or pulse width is less than a full 16-bit counter overflow period, the measurement is very straightforward. In practice, however, software usually must keep track of the number of overflows of the 16-bit counter in order to extend the range.

Another typical use of the input capture function is to establish a time reference. In this case it may be used in conjunction with an output compare function in the same timer. For example, consider the case where it is required to generate an output signal transition a specific number of clock cycles after detecting an event (edge). The input capture function can be used to record the time at which the event occurred. A number corresponding to the desired delay can then be added to this captured value and stored in an output compare register. Because input capture and output compare functions are referenced to the same 16-bit counter, the delay can be controlled to the resolution of the free-running counter, independent of software latencies.

Figure 1-5 Simplified block diagram of 16-bit input capture

# 1.7 Output compare (OC) concepts

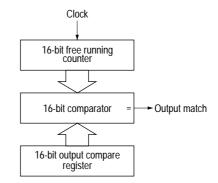

Output compare functions are used to cause events to occur at specific times, i.e. to cause signal transitions to occur on an output pin. A typical 16-bit output compare function is shown in Figure 1-6; it comprises a 16-bit compare register, a 16-bit comparator and a 16-bit free-running counter. When the value stored in the compare register matches the value of the free-running counter, the comparator sets an output compare flag.

Other events can occur when the output compare flag is set: an interrupt may be generated (if interrupts are enabled) and the logic levels on pins associated with the output compare function may change.

Figure 1-6 Simplified block diagram of 16-bit output compare

The output compare function can generate an output of a specific duration and polarity. A 16-bit value corresponding to the time a when a pin state change will occur is written to the output

compare register. The output compare function is configured to generate a high or low output automatically on the pin, or to toggle the state on the pin, when the match occurs. The output compare register is loaded with a new value after the compare occurs. Typically, more than one output compare function is associated with each pin; because pin state changes occur automatically at specific values of the free-running counter, the pulse width can be controlled to the resolution of the free-running counter independent of software latencies. A periodic pulse of a specific frequency and duty cycle can be generated by repeating the above steps.

## 1.8 Pulse accumulator (PA) concepts

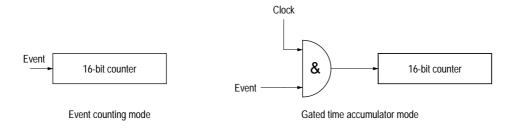

Pulse accumulator systems are usually based on 8 or 16 bits. A typical 16-bit pulse accumulator is shown in Figure 1-7; it consists of a 16-bit counter and edge select logic, and has two modes of operation: event counting mode and gated mode. In event counting mode, the counter is incremented each time an event occurs. In gated mode, an internal clock source increments the counter while a selected level is present on the input pin (the gate). When the signal on the input pin is negated, the counter is stopped. Two status flags are available: one to indicate the occurrence of an event, and the other to indicate counter overflow. Either of these flags can cause the processor to be interrupted.

The pulse accumulator can be used, for example, to count the number of items going by on a conveyor belt or the number of teeth that have gone by on a crankshaft timing gear. As each item or tooth is detected, the counter is incremented (event counting mode). The counter therefore contains the number of items (or teeth). The flag indicates the occurrence of an event (an item or tooth went by). If interrupts are enabled, an interrupt is generated. Software can read the counter at this time.

The gated mode of operation can be used to measure the pulse width or period of an input signal. When the input to the pulse accumulator is active, the counter begins counting the input clock. When the signal is negated it stops counting. If the counter is set to zero before the pulse starts, the count value multiplied by the clock period gives the width of the input pulse to the nearest clock period. This could be used to determine how long a stimulus is present.

In an 8-bit pulse accumulator only 255 events can be counted before the counter overflows; the overflow flag can be used to extend the counter range beyond this value if required.

## 1.9 Pulse width modulation (PWM) concepts

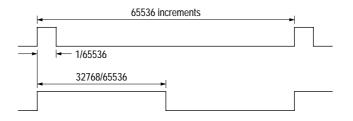

A PWM waveform is created when the mark-to-space ratio of a periodic rectangular signal can be varied. If the waveform can be incrementally changed by 1/65536 of its period, it has 16 bits of resolution (see Figure 1-8).

Figure 1-8 PWM example waveforms

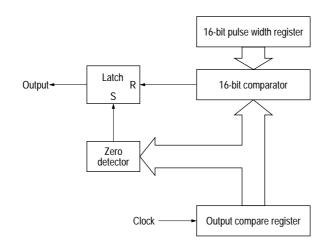

A typical 16-bit PWM system (Motorola's General Purpose Timer, or GPT) is shown in Figure 1-9. Each time the counter overflows from \$FFFF to \$0000, the zero detector sets the output latch (output pin in high state). The zero detector is used as the reference to start the high time. As the counter is incremented, the counter value is compared with the contents of the pulse width register. When the comparator detects a match, the latch is reset. By changing the value in the pulse width register, the duty cycle is continuously variable in 1/65536 increments.

If the pulse width register contains \$0000, the output latch will always be in the reset condition (output pin in low state). If the pulse width register is loaded with \$0001, the output latch will be set for one count before being reset for the remainder of the period. If the register contains \$8000 (32768 in decimal), the latch will be set for 32768 counts of the timer before being reset, resulting in a duty cycle of 50%. Provision is usually made to allow a 100% duty cycle (output latch always set; output pin always high) to be generated.

Varying the input clock frequency to the PWM counter also varies the period of the PWM signal.

Figure 1-9 Simplified block diagram of a typical 16-bit PWM system

Typically, PWM systems are provided with increased flexibility via additional features such as output polarity selection, variable resolution and variable pulse periods.

# 1.10 Using and clearing flag bits

To clear any flag bit in the CTM, the software must first read the register containing the flag in question (usually the SIC register), then write a zero to the flag bit. These two steps do not have to be done on consecutive instructions. Writing a one to the flag bit has no effect.

*Note:* The flag clearing mechanism will work only if no flag setting event occurs between the read and write operations; if a flag setting event occurs between the read and write operations, the flag bit will not be cleared.

# 2

# **BUS INTERFACE UNIT SUBMODULE (BIUSM)**

#### 2.1 BIUSM description

The BIUSM connects the CTM's SMB to the IMB and allows the CTM submodules to communicate with the bus master (usually a CPU). The BIUSM also communicates interrupt requests, from the CTM submodules to the IMB, and transfers the interrupt level, arbitration bit and vector number to the CPU during the interrupt acknowledge cycle. The BIUSM contains a module configuration register, a time base bus register and a test register (for factory testing only).

## 2.2 Freeze action on the BIUSM

When the IMB freeze condition is detected, the FRZ bit in the BIUSM module configuration register determines whether or not the freeze condition is passed on to the other CTM submodules. If FRZ = 0, the freeze condition is ignored; if FRZ = 1, the BIUSM passes the FREEZE signal from the IMB through to the CTM submodules. Each CTM submodule then reacts to the FREEZE signal as defined by its own internal circuitry and control bits.

# 2.3 LPSTOP action on the BIUSM

When the CPU is stopped by an LPSTOP instruction (from CPU32 or CPU16), the system clock ( $f_{SYS}$ ) is stopped, thereby shutting down all dependent modules, including the CTM, until the low-power STOP mode is exited.

# 2.4 STOP and WAIT action on the BIUSM

When the STOP instruction on CPU32 or the WAIT instruction on CPU16 is executed, only the CPU is stopped; the CTM continues to operate as normal. (To stop the CTM operation selectively, refer to the description of the STOP bit in Section 2.5.1).

## 2.5 BIUSM registers

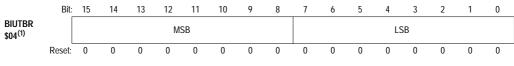

The BIUSM register map comprises four 16-bit register locations. As shown in Table 2-1, the register block contains the three BIUSM registers and one reserved register. The BIUSM register block always occupies the first four register locations in the CTM register space and cannot be relocated within the CTM structure. All unused bits and reserved address locations return zero when read by the software. Writing to unused bits and reserved address locations has no effect.

*Note:* All BIUSM register addresses in this section are specified as offsets from the base address of the CTM.

| Address <sup>(1)</sup> | 15 | 8 7                                          | 0 |

|------------------------|----|----------------------------------------------|---|

| \$00                   |    | BIUSM module configuration register (BIUMCR) |   |

| \$02                   |    | BIUSM test register (BIUTEST)                |   |

| \$04                   |    | BIUSM time base register (BIUTBR)            |   |

| \$06                   |    |                                              |   |

(1) Offset from the base address of the CTM.

# 2.5.1 BIUMCR — BIUSM module configuration register

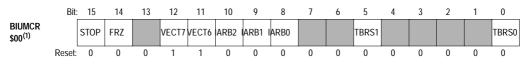

The BIUMCR register contains nine defined bits that allow the software to control five functions of the CTM: enabling/disabling of the module, response to FREEZE, vector base address, interrupt arbitration number and access to the time base buses (via the time base register).

(1) Offset from the base address of the CTM.

#### STOP — Stop enable

The STOP bit, while asserted, activates the FREEZE signal on the SMB regardless of the state of the FREEZE signal on the IMB. This completely stops the operation of the CTM. Note that some submodules may validate this signal with internal enable bits. The BIUSM continues to operate to allow the CPU access to the submodule's registers. The SMB FREEZE signal remains active until reset or until the STOP bit is negated by the CPU (via the IMB).

The STOP bit is cleared by reset.

- 1 (set) Stops operation of the CTM.

- 0 (clear) Allows operation of the CTM.

#### FRZ — Freeze enable

The FRZ bit, while asserted, activates the FREEZE signal on the SMB when the FREEZE signal on the IMB is active. This completely stops the operation of the CTM. Note that some submodules may validate this signal with internal enable bits. The BIUSM continues to operate to allow the CPU access to the submodule's registers. The SMB FREEZE signal remains active until the FRZ bit is cleared or the IMB FREEZE signal is negated.

The FRZ bit is cleared by reset.

- 1 (set) Halts the CTM sub module when the FREEZE signal appears on the IMB.

- 0 (clear) Ignores the FREEZE signal on the IMB.

#### VECT7, VECT6 — Interrupt vector base number bits

The interrupt vector base number bits select the interrupt vector base number for the CTM. Of the 8 bits necessary for vector number definition, the six least significant bits are programmed by hardware on a submodule basis, while the two remaining bits are provided by VECT7 and VECT6. This places the CTM vectors in one of four possible positions in the interrupt vector table, as follows.

| VECT7 | VECT6 | Resulting vector<br>base number |

|-------|-------|---------------------------------|

| 0     | 0     | \$00                            |

| 0     | 1     | \$40                            |

| 1     | 0     | \$80                            |

| 1     | 1     | \$C0                            |

*Note:* The reader should refer also to Section 3.4 and to the relevant CPU reference manuals for more detailed information on interrupt vector tables.

#### IARB[2:0] — Interrupt arbitration identification bits

The interrupt arbitration bit field (IARB), composed of IARB[2:0] in the BIUMCR and the IARB3 bit within each submodule, provides fifteen different arbitration identification numbers that can be used to arbitrate between interrupt requests occurring on the IMB with the same interrupt priority level.