# QADC QUEUED ANALOG-TO-DIGITAL CONVERTER REFERENCE MANUAL

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. MOTOROLA and the Motorola logo are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© MOTOROLA, INC. 1995, 1996

# PREFACE

This manual describes the capabilities, operation, and functions of the queued analogto-digital converter (QADC). The following conventions are used throughout the manual.

Logic level one is the voltage that corresponds to Boolean true (1) state.

Logic level zero is the voltage that corresponds to Boolean false (0) state.

To set a bit or bits means to establish logic level one on the bit or bits.

To **clear** a bit or bits means to establish logic level zero on the bit or bits.

A signal that is **asserted** is in its active logic state. An active low signal changes from logic level one to logic level zero when asserted, and an active high signal changes from logic level zero to logic level one.

A signal that is **negated** is in its inactive logic state. An active low signal changes from logic level zero to logic level one when negated, and an active high signal changes from logic level one to logic level zero.

**LSB** means least significant bit or bits. **MSB** means most significant bit or bits. References to low and high bytes are spelled out.

A **specific bit or signal** within a range is referred to by mnemonic and number. For example, ADDR15 is bit 15 of the address bus. **A range of bits or signals** is referred to by mnemonic and the numbers that define the range. For example, DATA[7:0] form the low byte of the data bus.

l

# TABLE OF CONTENTS

#### Paragraph

Title

Page

# **SECTION 1 OVERVIEW**

| 1.1 | Block Diagram1-1 |

|-----|------------------|

| 1.2 | QADC Features1-2 |

| 1.3 | Memory Map1-2    |

## **SECTION 2 SIGNAL DESCRIPTIONS**

| Port A Pin Functions             | .2-2                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port A Analog Input Pins         | .2-2                                                                                                                                                                                                                                                                                                                                      |

| Port A Digital Input/Output Pins | .2-2                                                                                                                                                                                                                                                                                                                                      |

| Port B Pin Functions             | .2-2                                                                                                                                                                                                                                                                                                                                      |

| Port B Analog Input Pins         | .2-2                                                                                                                                                                                                                                                                                                                                      |

| Port B Digital Input Pins        |                                                                                                                                                                                                                                                                                                                                           |

| External Trigger Input Pins      | .2-3                                                                                                                                                                                                                                                                                                                                      |

| Multiplexed Address Output Pins  |                                                                                                                                                                                                                                                                                                                                           |

| Multiplexed Analog Input Pins    | .2-3                                                                                                                                                                                                                                                                                                                                      |

| Voltage Reference Pins           | .2-4                                                                                                                                                                                                                                                                                                                                      |

| Dedicated Analog Supply Pins     | .2-4                                                                                                                                                                                                                                                                                                                                      |

| External Digital Supply Pin      | .2-4                                                                                                                                                                                                                                                                                                                                      |

| Internal Digital Supply Pins     | .2-4                                                                                                                                                                                                                                                                                                                                      |

|                                  | Port A Analog Input Pins<br>Port A Digital Input/Output Pins<br>Port B Pin Functions<br>Port B Analog Input Pins<br>Port B Digital Input Pins<br>External Trigger Input Pins<br>Multiplexed Address Output Pins<br>Multiplexed Analog Input Pins<br>Voltage Reference Pins<br>Dedicated Analog Supply Pins<br>External Digital Supply Pin |

# **SECTION 3 CONFIGURATION AND CONTROL**

| QADC Bus Interface Unit               | 3-1                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QADC Bus Accessing                    | 3-1                                                                                                                                                                                                                                                                                                                                            |

| Module Configuration                  | 3-3                                                                                                                                                                                                                                                                                                                                            |

| Low Power Stop Mode                   | 3-3                                                                                                                                                                                                                                                                                                                                            |

| Freeze Mode                           | 3-4                                                                                                                                                                                                                                                                                                                                            |

| Supervisor/Unrestricted Address Space | 3-4                                                                                                                                                                                                                                                                                                                                            |

| Interrupt Arbitration Priority        | 3-5                                                                                                                                                                                                                                                                                                                                            |

| QADC Module Configuration Register    | 3-5                                                                                                                                                                                                                                                                                                                                            |

| QADC Test Register                    | 3-6                                                                                                                                                                                                                                                                                                                                            |

| General-Purpose I/O Port Operation    | 3-6                                                                                                                                                                                                                                                                                                                                            |

| Port Data Register                    | 3-6                                                                                                                                                                                                                                                                                                                                            |

| Port Data Direction Register          | 3-7                                                                                                                                                                                                                                                                                                                                            |

|                                       | QADC Bus Interface Unit<br>QADC Bus Accessing<br>Module Configuration<br>Low Power Stop Mode<br>Freeze Mode<br>Supervisor/Unrestricted Address Space<br>Interrupt Arbitration Priority<br>QADC Module Configuration Register<br>QADC Test Register<br>General-Purpose I/O Port Operation<br>Port Data Register<br>Port Data Direction Register |

# **SECTION 4 EXTERNAL MULTIPLEXING**

| 4.1 | External Multiplexing Operation | 4-1 |

|-----|---------------------------------|-----|

| 4.2 | Module Version Options          | 4-3 |

#### TABLE OF CONTENTS (Continued) Title

Paragraph

#### Page

#### **SECTION 5 PIN CONNECTION CONSIDERATIONS**

| 5.1   | Analog Reference Pins                             | 5-1  |

|-------|---------------------------------------------------|------|

| 5.2   | Analog Power Pins                                 |      |

| 5.3   | Analog Supply Filtering and Grounding             |      |

| 5.4   | Accommodating Positive/Negative Stress Conditions |      |

| 5.5   | Analog Input Considerations                       | 5-6  |

| 5.6   | Analog Input Pins                                 | 5-8  |

| 5.6.1 | Settling Time for the External Circuit            | 5-9  |

| 5.6.2 | Error Resulting from Leakage                      | 5-10 |

## **SECTION 6 ANALOG SUBSYSTEM**

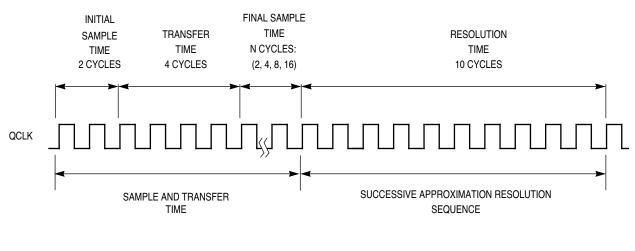

| 6.1     | Analog-to-Digital Converter Operation   | 6-1 |

|---------|-----------------------------------------|-----|

| 6.1.1   | Conversion Cycle Times                  | 6-2 |

| 6.1.1.1 | Amplifier Bypass Mode Conversion Timing |     |

| 6.2     | Front-End Analog Multiplexer            |     |

| 6.3     | Digital to Analog Converter Array       | 6-3 |

| 6.4     | Comparator                              | 6-4 |

| 6.5     | Successive Approximation Register       | 6-4 |

## **SECTION 7 DIGITAL CONTROL**

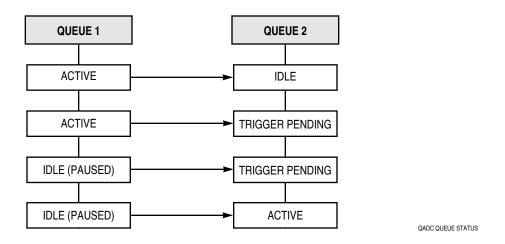

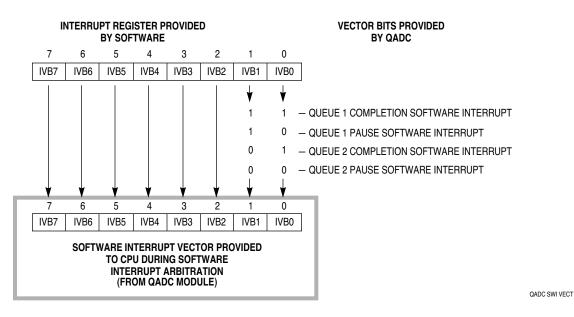

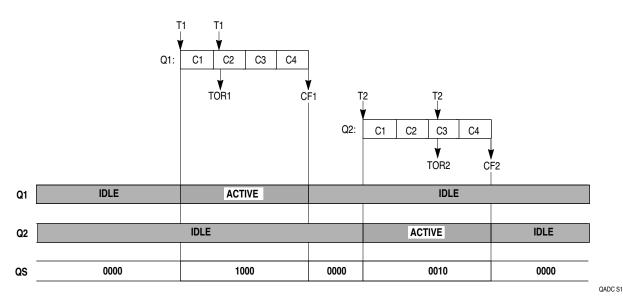

| 7.1     | Queue Priority                          | 7-1  |

|---------|-----------------------------------------|------|

| 7.2     | Boundary Conditions                     | 7-3  |

| 7.3     | Scan Modes                              | 7-4  |

| 7.3.1   | Disabled Mode and Reserved Mode         | 7-4  |

| 7.3.2   | Single-Scan Modes                       | 7-4  |

| 7.3.2.1 | Software Initiated Single-Scan Mode     | 7-5  |

| 7.3.2.2 | External Trigger Single-Scan Mode       | 7-6  |

| 7.3.2.3 | Interval Timer Single-Scan Mode         | 7-6  |

| 7.3.3   | Continuous-Scan Modes                   | 7-7  |

| 7.3.3.1 | Software Initiated Continuous-Scan Mode | 7-8  |

| 7.3.3.2 | External Trigger Continuous-Scan Mode   | 7-9  |

| 7.3.3.3 | Periodic Timer Continuous-Scan Mode     | 7-9  |

| 7.4     | QADC Clock (QCLK) Generation            | 7-9  |

| 7.5     | Periodic/Interval Timer                 |      |

| 7.6     | Control and Status Registers            | 7-14 |

| 7.6.1   | Control Register 0                      | 7-14 |

| 7.6.2   | Control Register 1                      | 7-16 |

| 7.6.3   | Control Register 2                      |      |

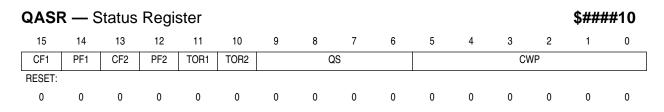

| 7.6.4   | Status Register                         | 7-20 |

|         |                                         |      |

#### **TABLE OF CONTENTS** (Continued)

Title

# Paragraph

#### Page

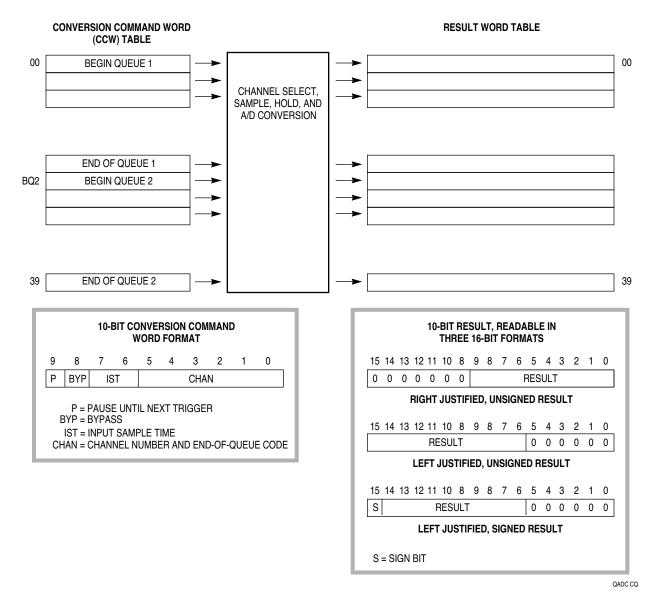

| 7.7 | Conversion Command Word Table7-26 | 3 |

|-----|-----------------------------------|---|

| 7.8 | Result Word Table7-32             | 2 |

#### **SECTION 8 INTERRUPTS**

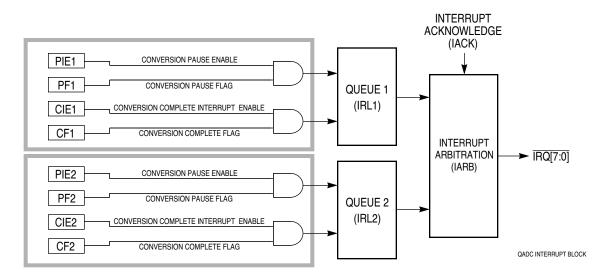

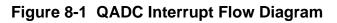

| 8.1 | Interrupt Operation                                  | .8-1  |

|-----|------------------------------------------------------|-------|

| 8.2 | Polled and Interrupt-Driven Operation                |       |

| 8.3 | Interrupt Sources                                    |       |

| 8.4 | QADC Interrupt Register                              | .8-2  |

| 8.5 | Interrupt Priority                                   | .8-3  |

| 8.6 | Interrupt Arbitration                                | .8-4  |

| 8.7 | Interrupt Vectors                                    | .8-4  |

| 8.8 | Initializing the QADC for Interrupt Driven Operation | . 8-5 |

| 8.9 | Interrupt Processing Summary                         | .8-6  |

#### **SECTION 9 QUEUE PRIORITY EXAMPLES**

| 9.1 | Queue Priority Schemes |  |

|-----|------------------------|--|

|-----|------------------------|--|

## **APPENDIX A ELECTRICAL CHARACTERISTICS**

# APPENDIX B REGISTER SUMMARY

| B.1   | Address Map                        | B-1  |

|-------|------------------------------------|------|

| B.2   | QADC Registers                     | B-1  |

| B.2.1 | QADC Module Configuration Register | B-1  |

| B.2.2 | QADC Test Register                 | B-2  |

| B.2.3 | QADC Interrupt Register            | B-2  |

| B.2.4 | Port A/B Data Register             | B-3  |

| B.2.5 | Port Data Direction Register       | B-3  |

| B.2.6 | QADC Control Registers             | B-4  |

| B.2.7 | QADC Status Register               | B-7  |

| B.2.8 | Conversion Command Word Table      | B-8  |

| B.2.9 | Result Registers                   | B-11 |

|       | -                                  |      |

# **APPENDIX C CONVERSION ACCURACY DEFINITIONS**

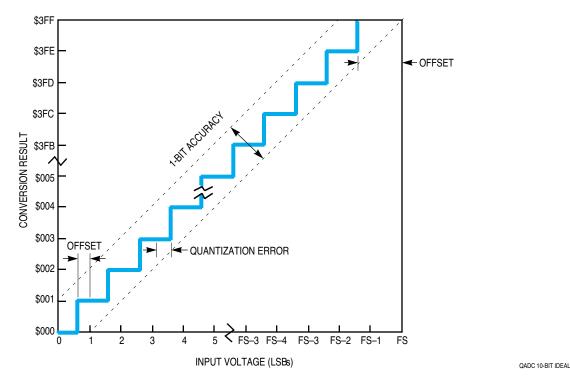

| C.1 | Transfer Curve           | C-1 |

|-----|--------------------------|-----|

| C.2 | Offset Error             | C-2 |

|     | Quantizing Error         |     |

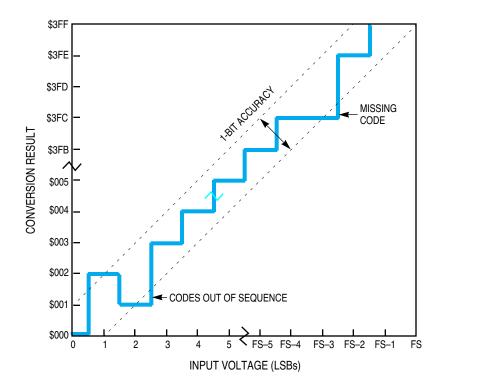

|     | Monotonicity             |     |

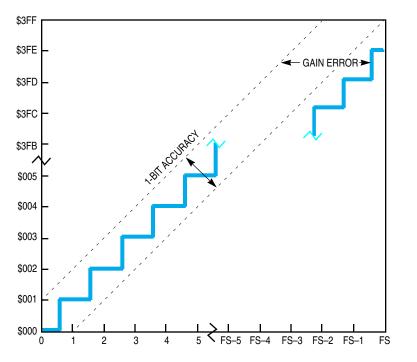

| C.5 | Gain Error (Slope Error) |     |

| C.6 | Integral Non-Linearity   |     |

#### TABLE OF CONTENTS

#### TABLE OF CONTENTS (Continued) Title

# Paragraph

Page

C.7 Differential Non-Linearity (Related to Monotonicity) ...... C-4

INDEX

# LIST OF ILLUSTRATIONS

| Figure | Title                                                | Page |

|--------|------------------------------------------------------|------|

| 1-1    | QADC Block Diagram                                   |      |

| 2-1    | QADC Input and Output Signals                        |      |

| 3-1    | Bus Cycle Accesses                                   |      |

| 4-1    | Example of External Multiplexing                     |      |

| 5-1    | Analog Input Circuitry                               |      |

| 5-2    | Errors Resulting from Clipping                       |      |

| 5-3    | Star-Ground at the Point of Power Supply Origin      |      |

| 5-4    | Input Pin Subjected to Negative Stress               |      |

| 5-5    | Voltage Limiting Diodes in a Negative Stress Circuit |      |

| 5-6    | External Multiplexing Of Analog Signal Sources       |      |

| 5-7    | Electrical Model of an A/D Input Pin                 |      |

| 6-1    | QADC Module Block Diagram                            |      |

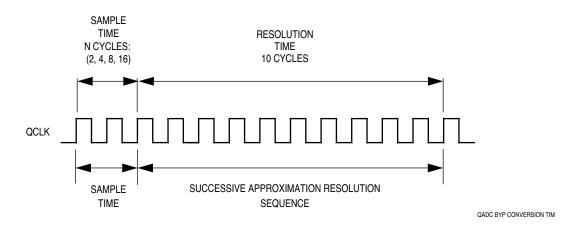

| 6-2    | Conversion Timing                                    |      |

| 6-3    | Bypass Mode Conversion Timing                        |      |

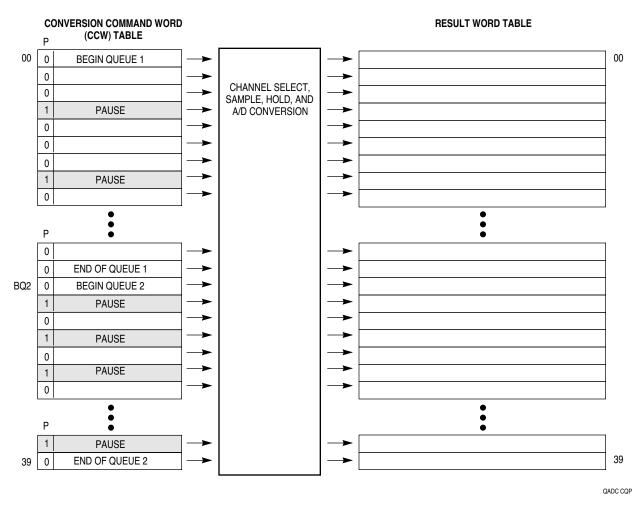

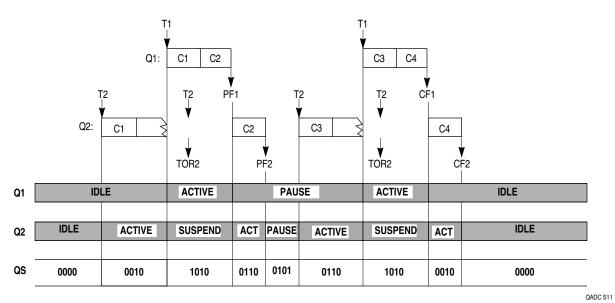

| 7-1    | QADC Queue Operation With Pause                      |      |

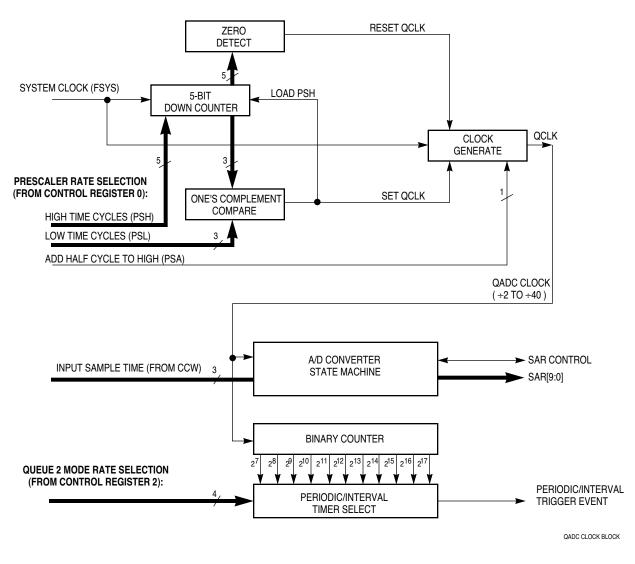

| 7-2    | QADC Clock Subsystem Functions                       |      |

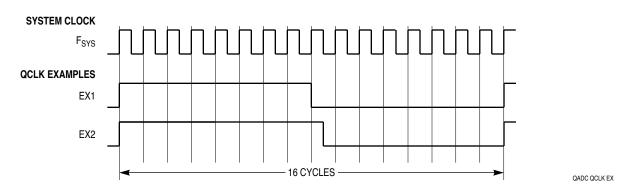

| 7-3    | QADC Clock Programmability Examples                  |      |

| 7-4    | Queue Status Transition                              |      |

| 7-5    | QADC Conversion Queue Operation                      |      |

| 8-1    | QADC Interrupt Flow Diagram                          |      |

| 8-2    | QADC Interrupt Vector Format                         |      |

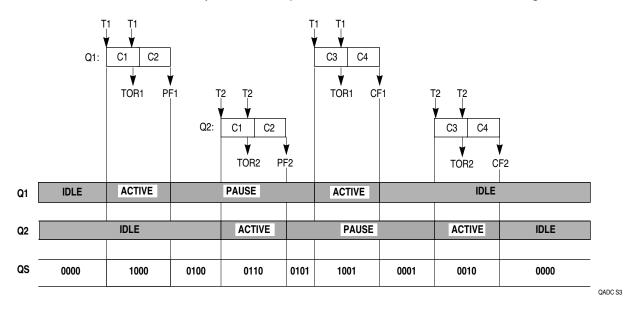

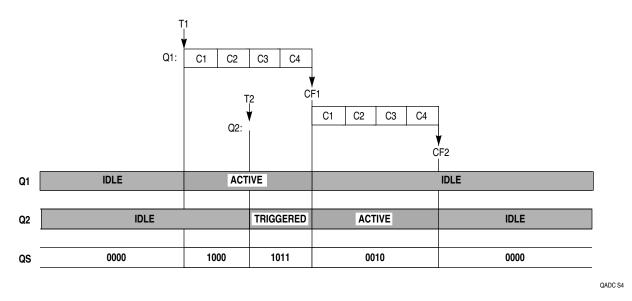

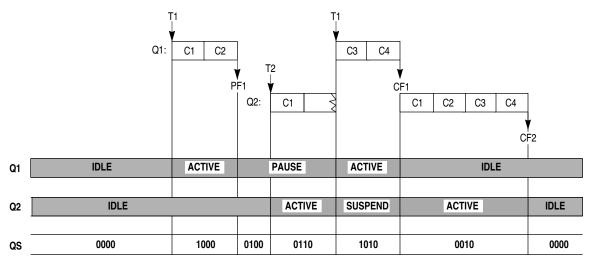

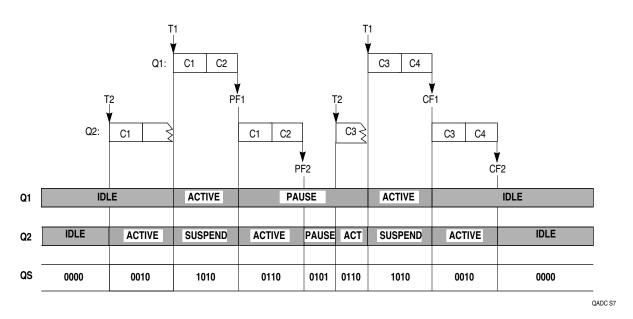

| 9-1    | CCW Priority Situation 1                             |      |

| 9-2    | CCW Priority Situation 2                             |      |

| 9-3    | CCW Priority Situation 3                             |      |

| 9-4    | CCW Priority Situation 4                             |      |

| 9-5    | CCW Priority Situation 5                             |      |

| 9-6    | CCW Priority Situation 6                             |      |

| 9-7    | CCW Priority Situation 7                             |      |

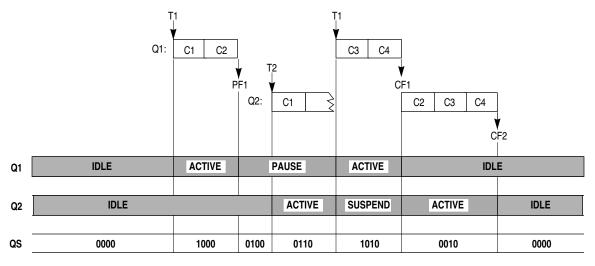

| 9-8    | CCW Priority Situation 8                             |      |

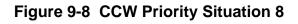

| 9-9    | CCW Priority Situation 9                             |      |

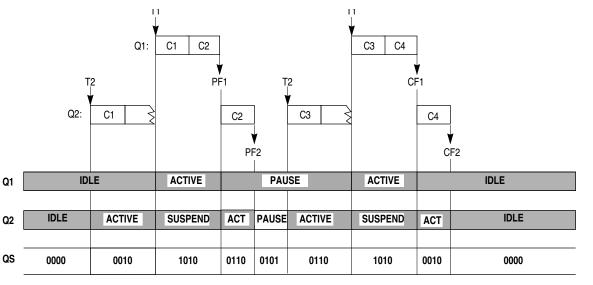

| 9-10   | CCW Priority Situation 10                            |      |

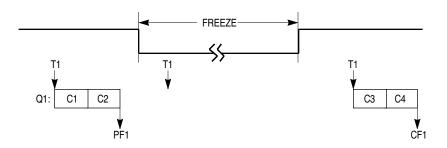

| 9-11   | CCW Priority Situation 11                            |      |

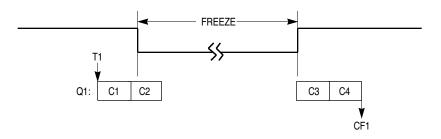

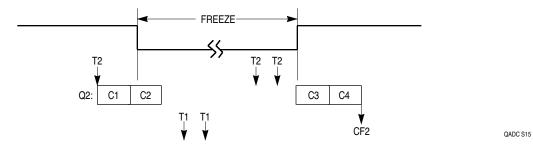

| 9-12   | CCW Freeze Situation 12                              |      |

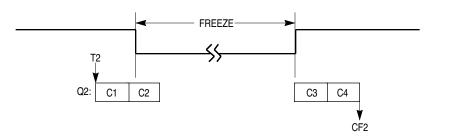

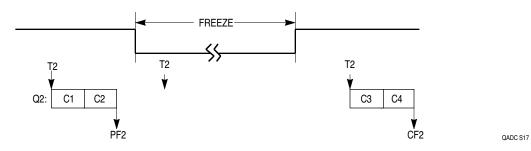

| 9-13   | CCW Freeze Situation 13                              |      |

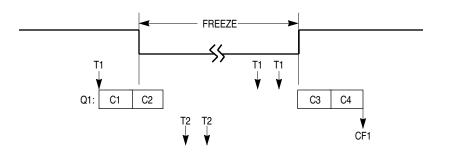

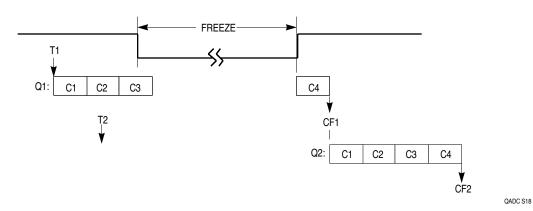

| 9-14   | CCW Freeze Situation 14                              |      |

| 9-15   | CCW Freeze Situation 15                              |      |

| 9-16   | CCW Freeze Situation 16                              |      |

| 9-17   | CCW Freeze Situation 17                              |      |

| 9-18   | CCW Freeze Situation 18                              |      |

| 9-19   | CCW Freeze Situation 19                              |      |

| C-1    | Transfer Curve of an Ideal 10-Bit A/D Converter      | C-1  |

# LIST OF ILLUSTRATIONS (Continued) Title

# Figure

# Page

| C-2 | Transfer Curve of a Non-Monotonic 10-Bit A/D Converter               | C-2 |

|-----|----------------------------------------------------------------------|-----|

| C-3 | Transfer Curve of a 10-Bit A/D Converter with Gain Error             | C-3 |

| C-4 | Transfer Curve of a 10-Bit A/D Converter With Integral > One LSB     | C-4 |

| C-5 | Transfer Curve of a 10-Bit A/D Converter With Differential Linearity | C-5 |

# LIST OF TABLES

Title

| Tab | le Title                                                | Page |

|-----|---------------------------------------------------------|------|

| 1-1 | QADC Address Map                                        |      |

| 2-1 | Multiplexed Analog Input Channels                       |      |

| 4-1 | Analog Input Channels                                   |      |

| 5-1 | External Circuit Settling Time (10-Bit Conversions)     |      |

| 5-2 | Error Resulting From Input Leakage (IOFF)               |      |

|     | QADC Clock Programmability                              |      |

| 7-2 | Prescaler Clock High Times                              |      |

| 7-3 | Prescaler Clock Low Times                               |      |

| 7-4 | Queue 1 Operating Modes                                 | 7-17 |

| 7-5 | Queue 2 Operating Modes                                 |      |

|     | Queue Status                                            |      |

|     | Input Sample Times                                      |      |

|     | Nonmultiplexed Channel Assignments and Pin Designations |      |

|     | Multiplexed Channel Assignments and Pin Designations    |      |

|     | QADC Status Flags and Interrupt Sources                 |      |

| 9-1 | Trigger Events                                          |      |

|     | Status Bits                                             |      |

|     | QADC Maximum Ratings                                    |      |

|     | QADC DC Electrical Characteristics (Operating)          |      |

|     | QADC AC Electrical Characteristics (Operating)          |      |

|     | QADC Conversion Characteristics (Operating)             |      |

|     | QADC Address Map                                        |      |

|     | Prescaler Clock High Times                              |      |

|     | Prescaler Clock Low Times                               |      |

|     | Queue 1 Operating Modes                                 |      |

|     | Queue 2 Operating Modes                                 |      |

|     | Queue Status                                            |      |

|     | Input Sample Times                                      |      |

|     | Nonmultiplexed Channel Assignments and Pin Designations |      |

| B-9 | Multiplexed Channel Assignments and Pin Designations    | B-10 |

Table

# **SECTION 1 OVERVIEW**

The queued analog-to-digital converter (QADC) is a 10-bit, unipolar, successive approximation converter. A maximum of 16 analog input channels can be supported using internal multiplexing. A maximum of 44 input channels can be supported in the expanded, externally multiplexed mode. The actual number of channels depends upon the number of pins available to the QADC module.

#### 1.1 Block Diagram

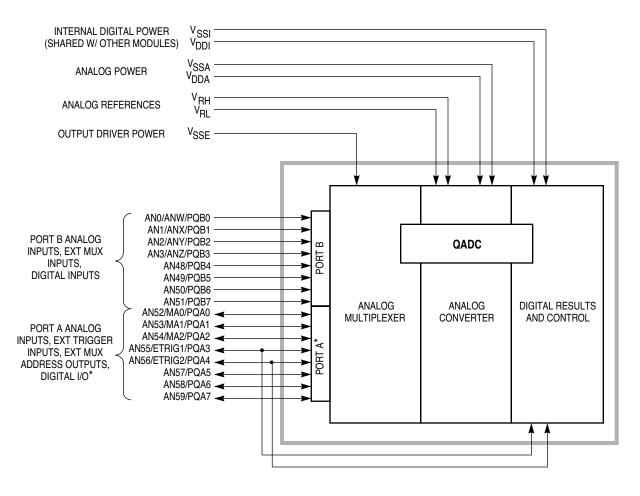

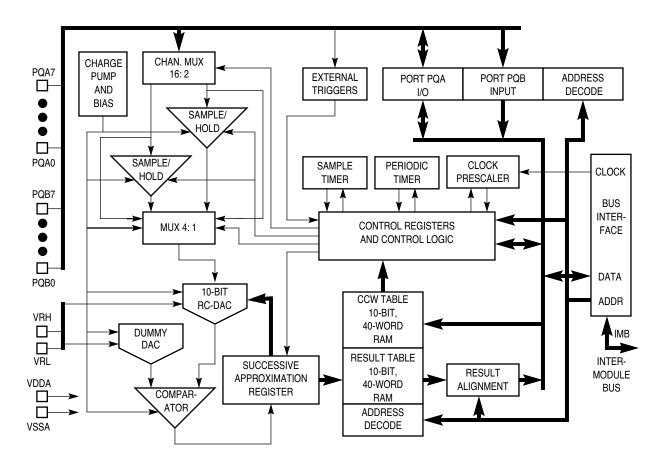

**Figure 1-1** displays the major components of the QADC module. The QADC consists of an analog front-end and a digital control subsystem, which includes an intermodule bus (IMB) interface block.

Figure 1-1 QADC Block Diagram

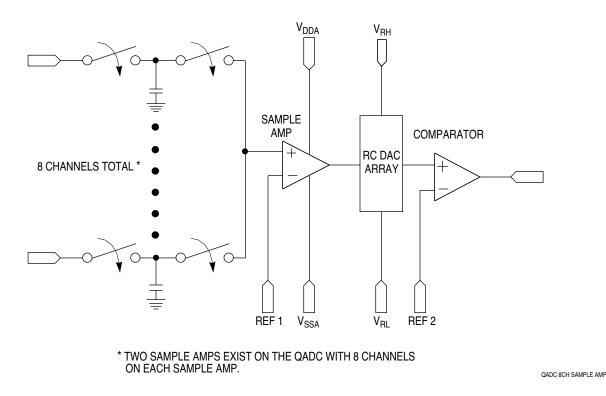

The analog section includes input pins, an analog multiplexer, and two sample and hold analog circuits. The analog conversion is performed by the digital-to-analog converter (DAC) resistor-capacitor array and a high-gain comparator.

The digital control section contains control logic to sequence the conversion process, channel select logic, and a successive approximation register (SAR). Also included are the periodic/interval timer, control and status registers, the conversion command word (CCW) table RAM, and the result word table RAM.

The bus interface unit (BIU) allows the QADC to operate with the applications software through the IMB environment.

# 1.2 QADC Features

- Sample and hold

- Up to 16 analog input channels using internal multiplexing

- Directly supports up to four external multiplexers (for example, the MC14051)

- Up to 44 total input channels with internal and external multiplexing

- Programmable input sample time for various source impedances

- Two conversion command queues of variable length

- Sub-queues possible using pause mechanism

- Queue complete and pause software interrupts available on both queues

- Automated queue modes initiated by:

- External trigger

- Periodic/interval timer, within QADC module

- Software command

- Single-scan or continuous-scan of queues

- 40 result registers

- Output data readable in three formats:

- Right-justified unsigned

- Left-justified signed

- Left-justified unsigned

- Unused analog channels can be used as digital ports

# 1.3 Memory Map

The QADC occupies 512 bytes, or 256 words, of address space. Nine words are control, port, and status registers, 40 words are the CCW table, and 40 words are the result word table which occupy 120 address locations because the result data is readable in three data alignment formats. The remaining words are reserved for expansion. **Table 1-1** displays the QADC memory map.

Each register address in **Table 1-1** consists of a 15-bit base address plus a 9-bit offset. The offset represents the nine low order bits of register address. "\$####" represents the 15-bit base address plus the high order bit of the offset. (For example, both LJUR and RJUR registers are represented by \$####B0-\$####FE, even though they represent different addresses since each register has a different most significant bit in their offset). For the precise locations of these registers, refer to the appropriate microcontroller unit (MCU) manual. The column labeled "Access" specifies which address space is designated supervisor data space or unrestricted data space. Remember that the MSB is determined by the MM bit.

| Access           | Address               | Offset          | 15 8 7 0                                                               |

|------------------|-----------------------|-----------------|------------------------------------------------------------------------|

| S <sup>1</sup>   | \$####00              | \$000           | MODULE CONFIGURATION REGISTER (QADCMCR)                                |

| S                | \$####02              | \$002           | TEST REGISTER (QADCTEST)                                               |

| S                | \$####04              | \$004           | INTERRUPT REGISTER (QADCINT)                                           |

| S/U <sup>2</sup> | \$####06              | \$006           | PORT A DATA (PORTQA) PORT B DATA (PORTQB)                              |

| S/U              | \$####08              | \$008           | PORT DATA DIRECTION REGISTER (DDRQA)                                   |

| S/U              | \$####0A              | \$00A           | CONTROL REGISTER 0 (QACR0)                                             |

| S/U              | \$####0C              | \$00C           | CONTROL REGISTER 1 (QACR1)                                             |

| S/U              | \$####0E              | \$00E           | CONTROL REGISTER 2 (QACR2)                                             |

| S/U              | \$####10              | \$010           | STATUS REGISTER (QASR)                                                 |

| —                | \$####12–<br>\$####2E | \$012–<br>\$02E | RESERVED                                                               |

| S/U              | \$####30–<br>\$####7E | \$030–<br>\$07E | CONVERSION COMMAND WORD (CCW) TABLE                                    |

| _                | \$####80–<br>\$####AE | \$080–<br>\$0AE | RESERVED                                                               |

| S/U              | \$####B0–<br>\$####FE | \$0B0<br>\$0FE  | RESULT WORD TABLE<br>RIGHT JUSTIFIED, UNSIGNED RESULT REGISTER (RJURR) |

| _                | \$####00–<br>\$####2E | \$100–<br>\$12E | RESERVED                                                               |

| S/U              | \$####30–<br>\$####7E | \$130–<br>\$17E | RESULT WORD TABLE<br>LEFT JUSTIFIED, SIGNED RESULT REGISTER (LJSRR)    |

| _                | \$####80–<br>\$####AE | \$180–<br>\$1AE | RESERVED                                                               |

| S/U              | \$####B0–<br>\$####FE | \$1B0–<br>\$1FE | RESULT WORD TABLE<br>LEFT JUSTIFIED, UNSIGNED RESULT REGISTER (LJURR)  |

# Table 1-1 QADC Address Map

NOTES:

1. S = Supervisor only

2. S/U = Unrestricted or supervisor depending on the state of the SUPV bit in the QADCMCR.

Access to supervisor-only data space is permitted only when the software is operating in supervisor access mode. Assignable data space can be either restricted to supervisor-only access or unrestricted to both supervisor and user data space addresses. The SUPV bit in the module configuration register designates the assignable space as supervisor or unrestricted.

Attempts to read a supervisor-only data space when not in the supervisor access mode causes a value of \$0000 to be returned. Attempts to read assignable data space in the unrestricted access mode when the space is programmed as supervisor space causes a value of \$FFFF to be returned. Attempts to write supervisor-only or supervisor-assigned data space when in the unrestricted access mode has no effect.

The CPU32 indicates the supervisor and user space access with the function code signal FC2 on the IMB bus. CPU16 does not support supervisor/user space selection, and is always in the supervisor access mode. In such cases, the SUPV bit has no meaning or effect.

The first block of the address map contains the nine words used for control, status, port, and test information. The control registers permit the software to initialize the QADC for the desired configuration and queue operating mode. Also included are the status bits that the software may read to identify an interrupt source and to determine

other information about the operation of the QADC. Refer to **APPENDIX B REGISTER SUMMARY** for more information.

The QADC has three global registers for configuring module operation: the module configuration register (QADCMCR), the interrupt register (QADCINT), and a test register (QADCTEST). The global registers are always defined to be in supervisor-only data space. When the CPU supports the supervisor/user address data space designations, software can establish the global registers to be in supervisor data space and the remaining registers and tables to be in user space.

All QADC analog channel/port pins that are not used for analog input channels can be used as digital port pins. Port values are read/written by accessing the port A and B data registers (PORTQA and PORTQB). The digital port pins are specified as inputs or outputs by programming the port data direction register (DDRQA). Only port A uses open drain pull-down output drivers.

The remaining four registers in the control register block control the operation of the queuing mechanism, and provide a means of monitoring the operation of the QADC. Control register 0 (QACR0) contains hardware configuration information. Control register 1 (QACR1) is associated with queue 1, and control register 2 (QACR2) is associated with queue 2. The status register (QASR) provides visibility on the status of each queue and the particular conversion that is in progress.

Following the register block in the address map is the CCW table. There are 40 words to hold the desired analog conversion sequences. Each CCW is a 16-bit word, with ten implemented bits in four fields. Refer to **APPENDIX B REGISTER SUMMARY** for more information.

The final block of address space belongs to the result word table, which appears in three places in the memory map. Each result word table location holds one 10-bit conversion value. The software selects one of three data formats, which map the 10-bit result onto the 16-bit data bus by reading the address which produces the desired alignment. The first address block presents the result data in right justified format, the second block is presented in left justified signed format, and the third is presented in left justified unsigned format. Refer to **APPENDIX B REGISTER SUMMARY** for more information.

# **SECTION 2 SIGNAL DESCRIPTIONS**

The QADC uses a maximum of 21 external pins. There are 16 channel/port pins that can support up to 44 channels when external multiplexing is used (including internal channels). All of the channel pins can also be used as general-purpose digital port pins. In addition, there are also two analog reference pins, two analog submodule power pins, and one  $V_{SSE}$  pin for the open drain output drivers on port A.

The QADC allows external trigger inputs and the multiplexer outputs to be combined onto some of the channel pins. All of the channel pins are used for at least two functions, depending on the modes in use.

The following paragraphs describe QADC pin functions. **Figure 2-1** displays the QADC module pins.

\* PORT A PINS INCORPORATE OPEN DRAIN PULL DOWN DRIVERS.

QADC PINOUT

## Figure 2-1 QADC Input and Output Signals

# 2.1 Port A Pin Functions

The eight port A pins can be used as analog inputs, or as a bidirectional 8-bit digital input/output port. Refer to the following paragraphs for more information.

# 2.1.1 Port A Analog Input Pins

When used as analog inputs, the eight port A pins are referred to as AN[59:52]. Due to the digital output drivers associated with port A, the analog characteristics of port A are different from those of port B. Refer to **APPENDIX B REGISTER SUMMARY** for more information on analog signal characteristics. All of the analog signal input pins may be used for at least one other purpose.

# 2.1.2 Port A Digital Input/Output Pins

Port A pins are referred to as PQA[7:0] when used as a bidirectional 8-bit digital input/ output port. These eight pins may be used for general-purpose digital input signals or digital open drain pull-down output signals.

Port A pins are connected to a digital input synchronizer during reads and may be used as general purpose digital inputs when the applied voltages meet high voltage input ( $V_{IH}$ ) and low voltage input ( $V_{IL}$ ) requirements. Refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** for more information on voltage requirements.

Each port A pin is configured as an input or output by programming the upper half of the port data direction register (DDRQA). The digital input signal states are read by the software in the upper half of the port data register when the port data direction register specifies that the pins are inputs. The digital data in the port data register is driven onto the port A pins when the corresponding bit in the port data direction register specifies output. Refer to **APPENDIX B REGISTER SUMMARY** for more information. Since the outputs are open drain drivers (so as to minimize the effects to the analog function of the pins), active external pull-up provisions must be made when the output is used to drive another integrated circuit.

# 2.2 Port B Pin Functions

The eight port B pins can be used as analog inputs, or as an 8-bit digital input only port. Refer to the following paragraphs for more information.

# 2.2.1 Port B Analog Input Pins

When used as analog inputs, the eight port B pins are referred to as AN[51:48]/ AN[3:0]. Since port B functions as analog and digital input only, the analog characteristics are different from those of port A. Refer to **APPENDIX A ELECTRICAL CHAR**-**ACTERISTICS** for more information on analog signal characteristics. All of the analog signal input pins may be used for at least one other purpose.

# 2.2.2 Port B Digital Input Pins

Port B pins are referred to as PQB[7:0] when used as an 8-bit digital input only port. In addition to functioning as analog input pins, the port B pins are also connected to

the input of a synchronizer during reads and may be used as general-purpose digital inputs when the applied voltages meet  $V_{IH}$  and  $V_{IL}$  requirements. Refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** for more information on voltage requirements.

Since port B pins are input only, a data direction register is not necessary. The digital input signal states are read by the software in the lower half of the port data register. Refer to **APPENDIX B REGISTER SUMMARY** for more information.

# 2.3 External Trigger Input Pins

The QADC uses two external trigger pins (ETRIG[2:1]). The external trigger inputs are included in two multifunction port A pins (PQA[4:3]), which are normally used as analog channel input pins. Each of the two input external trigger pins is associated with one of the scan queues, queue 1 and queue 2. When a queue is in an external trigger mode, the corresponding external trigger pin is configured as a digital input and the software programmed input/output direction for the external trigger pins in the data direction register (DDRQA) is ignored. Refer to paragraph 7.7 in **SECTION 7 DIGITAL CONTROL** for more information.

# 2.4 Multiplexed Address Output Pins

In the non-multiplexed mode, the 16 channel pins are connected to an internal multiplexer which routes the analog signals into the internal A/D converter.

In the externally multiplexed mode, the QADC allows automatic channel selection through up to four external 8-to-1 selector chips. The QADC provides a 3-bit multiplexed address output to the external multiplex chips to allow selection of one of eight inputs. The multiplexed address output signals (MA[2:0]) can be used as multiplex address output bits, or as general I/O.

MA[2:0] are used as the address inputs for up to four 8-channel multiplexer chips (for example, the MC14051 and the MC74HC4051). Since the MA[2:0] pins are digital outputs in the multiplexed mode, the software programmed input/output direction for the multiplex address pins in the data direction register is ignored.

Refer to paragraph 7.7 in **SECTION 7 DIGITAL CONTROL** for more information on the use of multiplexed address output pins in the external multiplexed mode.

## 2.5 Multiplexed Analog Input Pins

In the external multiplexed mode, four of the port B pins are redefined to each represent eight input channels. Refer to **Table 2-1**.

| Multiplexed Analog Input | Channels                            |  |  |  |  |  |  |

|--------------------------|-------------------------------------|--|--|--|--|--|--|

| ANw                      | Even numbered channels from 0 to 14 |  |  |  |  |  |  |

| ANx                      | Odd numbered channels from 1 to 15  |  |  |  |  |  |  |

| ANy                      | Even channels from 16 to 30         |  |  |  |  |  |  |

| ANz                      | Odd channels from 17 to 31          |  |  |  |  |  |  |

# Table 2-1 Multiplexed Analog Input Channels

Refer to paragraph 7.7 in **SECTION 7 DIGITAL CONTROL** for more information.

# 2.6 Voltage Reference Pins

$V_{RH}$  and  $V_{RL}$  are the dedicated input pins for the high and low reference voltages. Separating the reference inputs from the power supply pins allows for additional external filtering, which increases reference voltage precision and stability, and subsequently contributes to a higher degree of conversion accuracy. Refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** for more information.

#### 2.7 Dedicated Analog Supply Pins

$V_{DDA}$  and  $V_{SSA}$  pins supply power to the analog subsystems of the QADC module. Dedicated power is required to isolate the sensitive analog circuitry from the normal levels of noise present on the digital power supply. Refer to **APPENDIX A ELECTRI-CAL CHARACTERISTICS** for more information.

#### 2.8 External Digital Supply Pin

Each port A pin includes a digital open drain output driver, as well as an analog input signal path and a digital input synchronizer. The  $V_{SSE}$  pin provides the ground level for the drivers on the port A pins. Since the QADC output pins have open drain type drivers, a dedicated  $V_{DDE}$  pin is not needed. Refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** for more information.

#### 2.9 Internal Digital Supply Pins

$V_{DDI}$  and  $V_{SSI}$  pins provide the power for the digital portions of the QADC, and for all other digital modules on the microcontroller chip. Since these pins are common to all modules, they are not counted as QADC pins. Refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** for more information.

# **SECTION 3 CONFIGURATION AND CONTROL**

The QADC module communicates with other microcontroller modules via the intermodule bus (IMB). The QADC bus interface unit (BIU) coordinates IMB activity with internal QADC bus activity. This section describes the operation of the BIU, IMB read/ write accesses to QADC memory locations, module configuration, and general-purpose I/O operation.

## 3.1 QADC Bus Interface Unit

The BIU is designed to act as a slave device on the IMB. The BIU has the following functions: to respond with the appropriate bus cycle termination, and to supply IMB interface timing to all internal module signals.

BIU components consist of IMB buffers, address match and module select logic, interrupt and arbitration logic, the BIU state machine, clock prescaler logic, data bus routing logic, and the interface to the internal module data bus.

The QADC responds to all IMB operations and signals, allowing byte, word, and long word addressable read and write operations in any addressable space.

#### NOTE

Normal accesses to the QADC require two clocks. However, if the CPU tries to access locations that are also accessible by the QADC while the QADC is accessing them, the QADC produces wait states. From one to four CPU wait states may be inserted by the QADC in the process of reading and writing.

#### **3.2 QADC Bus Accessing**

The QADC permits software access to 8-bit, 16-bit words, and 32-bit long words, at even and odd addresses, however, coherency (ensuring that all samples are taken consecutively in one scan) is not provided for accesses that require more than one bus cycle. For example, if a read of two consecutive word locations in a result area are made, the QADC could change one word in the result area between the bus cycles. There is no holding register for the second word. Refer to paragraph 7.6.3 in **SECTION 7 DIGITAL CONTROL** for more information on coherency. All read and write accesses that require more than one 16-bit access to complete occur as two or more independent bus cycles. These accesses include misaligned and long word accesses.

## NOTE

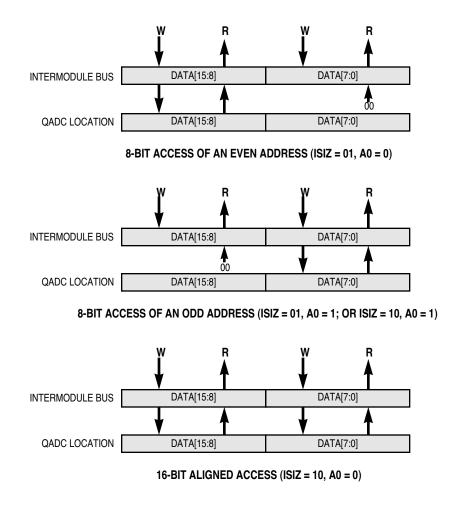

CPU32 does not support word access or long word access to an odd address. Both of these are considered misaligned accesses. The CPU16 supports misaligned and long word accesses. **Figure 3-1** shows the three bus cycles which are implemented by the QADC. The following paragraphs describe how the three types of accesses are used, including misaligned and long word accesses.

QADC BUS CYC ACC

Figure 3-1 Bus Cycle Accesses

Byte accesses to an even address read or write bits 15 through 8 of a QADC location, as shown in the top illustration of **Figure 3-1**. In the case of write cycles, bits 7 through 0 of the addressed QADC register are not disturbed. In the case of read cycles, the QADC provides zeros to the IMB for bits 7 through 0.

Byte accesses to an odd address read or write bits 7 through 0 of a QADC location, as shown in the center illustration of **Figure 3-1**. In the case of write cycles, bits 15 through 8 of the addressed QADC location are not disturbed. In the case of read cycles, the QADC provides zeros to the IMB for bits 15 through 8.

Word accesses to an even address read or write bits 15 through 0 of a QADC location, as shown in the lower illustration of **Figure 3-1**. A full 16 bits of data is written to and read from the QADC location with each access.

Word accesses to an odd address require two bus cycles; half of two different 16-bit QADC locations are accessed. The first bus cycle is treated by the QADC as an 8-bit read or write of an odd address. The second cycle is an 8-bit read or write of an even address. The QADC address space is organized into 16-bit even address locations, so a 16-bit read or write of an odd address obtains or provides the lower half of one QADC location, and the upper half of the following QADC location.

Long word (32-bit) accesses to an even address require two bus cycles to complete the access, and two full QADC locations are accessed. The first bus cycle reads or writes the addressed 16-bit QADC location and the second cycle reads or writes the following 16-bit location.

Long word accesses to an odd address require three bus cycles. Portions of three different QADC locations are accessed. The first bus cycle is treated by the QADC as an 8-bit access of an odd address, the second cycle is a 16-bit aligned access, and the third cycle is an 8-bit access of an even address. The QADC address space is organized into 16-bit even address locations, so a 32-bit read or write of an odd address provides the lower half of one QADC location, the full 16-bit content of the following QADC location, and the upper half of the third QADC location.

## 3.3 Module Configuration

The module configuration register (QADCMCR) contains parameters which allow the QADC to interface with other MCU modules. The register defines freeze and stop mode operation, supervisor-only access protection, and the QADC software interrupt arbitration priority number. The implemented fields can be read and written. Unimplemented locations read zero and writes have no effect. They are typically written once when the software initializes the QADC, and not changed afterwards.

# 3.3.1 Low Power Stop Mode

When the STOP bit in the QADCMCR is set, the clock signal to the A/D converter is disabled, effectively turning off the analog circuitry. This results in a static, low power consumption, idle condition. The stop mode aborts any conversion sequence in progress. Because the bias currents to the analog circuits are turned off in stop mode, the QADC requires some recovery time ( $T_{SR}$  in **APPENDIX A ELECTRICAL CHAR-ACTERISTICS**) to stabilize the analog circuits after the stop enable bit is cleared.

In the stop mode, the BIU state machine and logic do not shut down, and the QADC-MCR, the interrupt register (QADCINT), and the test register (QADCTEST) are fully accessible and are not reset. The data direction register (DDRQA), port data register (PORTQA/PORTQB), and control register 0 (QACR0) are not reset and are read-only accessible. The RAM is not reset and is not accessible. Control register 1 (QACR1), control register 2 (QACR2), and the status register (QASR) are reset and are read-only accessible. In addition, the QADC clock (QCLK) and the periodic/interval timer are held in reset during stop mode.

If the STOP bit is clear, stop mode is disabled.

#### 3.3.2 Freeze Mode

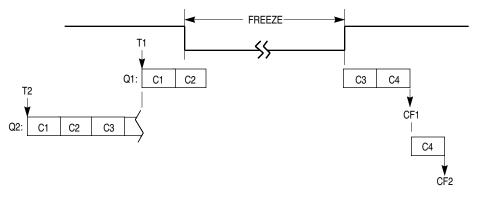

Freeze mode occurs when the background debug mode is enabled in the device integration module and a breakpoint is encountered. This is indicated by the assertion of the internal FREEZE line on the IMB. The FRZ bit in the QADCMCR determines whether or not the QADC responds to an IMB internal FREEZE signal assertion. Freeze is very useful when debugging an application.

When the FRZ bit is set, the QADC finishes any current conversion then freezes. Depending on when the FRZ bit is asserted, there are three possible queue "freeze" scenarios:

- When a queue is not executing, the QADC freezes immediately.

- When a queue is executing, the QADC completes the current conversion and then freezes.

- If during the execution of the current conversion, the queue operating mode for the active queue is changed, or a queue 2 abort occurs, the QADC freezes immediately.

When the QADC enters the freeze mode while a queue is active, the current CCW location of the queue pointer is saved.

During freeze, the analog clock is held in reset and is not clocked. Although QCLK is unaffected, the periodic/interval timer is held in reset. External trigger events that occur during the freeze mode are not recorded. The BIU remains active to allow IMB access to all QADC registers and RAM. Although the QADC saves a pointer to the next CCW in the current queue, the software can force the QADC to execute a different CCW by writing new queue operating modes for normal operation. The QADC looks at the queue operating modes, the current queue pointer, and any pending trigger events to decide which CCW to execute.

If the FRZ bit is clear, the internal FREEZE signal is ignored.

#### 3.3.3 Supervisor/Unrestricted Address Space

The QADC memory map is divided into two segments: supervisor-only data space and assignable data space. Access to supervisor-only data space is permitted only when the software is operating in supervisor access mode. Assignable data space can be either restricted to supervisor-only access or unrestricted to both supervisor and user data space accesses. The SUPV bit in the QADCMCR designates the assignable space as supervisor or unrestricted.

Attempts to read a supervisor-only data space when not in the supervisor access mode causes a value of \$0000 to be returned. Attempts to read assignable data space in the unrestricted access mode when the space is programmed as supervisor space causes a value of \$FFFF to be returned. Attempts to write supervisor-only or supervisor-assigned data space when in the unrestricted access mode has no effect.

The CPU indicates the supervisor and user space access with the function code bits (FC[2:0]) on the IMB bus.

#### NOTE

Some CPUs do not support supervisor/user space selection, and are always in the supervisor access mode. In such cases, the SUPV bit has no meaning or effect.

The supervisor-only data space segment contains the QADC global registers, which include the QADCMCR, the QADCTEST, and the QADCINT. The supervisor/unre-stricted space designation for the CCW table, the result word table, and the remaining QADC registers are programmable.

#### 3.3.4 Interrupt Arbitration Priority

Each module that can generate interrupts, including the QADC, has an IARB (interrupt arbitration number) field in the QADCMCR. Each IARB field must have a different value. During an interrupt acknowledge cycle, IARB permits arbitration among simultaneous interrupts of the same priority level.

The reset value of IARB in the QADCMCR is \$F. This prevents QADC interrupts from being discarded. Initialization software must set the IARB field to a lower value in the range \$F (highest priority) to \$1 (lowest priority) if lower priority interrupts are to be arbitrated.

Refer to **SECTION 8 INTERRUPTS** for more information.

#### 3.3.5 QADC Module Configuration Register

The QADCMCR contains fields and bits that control freeze and stop modes and determines the privilege level required to access most registers. It also contains the IARB field.

| QAD    | CMCF | R — № | lodule | e Con | figura | tion F | Regist | ter  |   |          |   |   |    | \$### | <b>##00</b> |  |

|--------|------|-------|--------|-------|--------|--------|--------|------|---|----------|---|---|----|-------|-------------|--|

| 15     | 14   | 13    | 12     | 11    | 10     | 9      | 8      | 7    | 6 | 5        | 4 | 3 | 2  | 1     | 0           |  |

| STOP   | FRZ  |       |        | NOT   | USED   |        |        | SUPV | 1 | NOT USED | ) |   | IA | RB    |             |  |

| RESET: |      |       |        |       |        |        |        |      |   |          |   |   |    |       |             |  |

| 0      | 0    |       |        |       |        |        |        | 1    |   |          |   | 0 | 0  | 0     | 0           |  |

STOP — Stop Enable

- 0 = Disable stop mode.

- 1 = Enable stop mode.

- FRZ Freeze Enable

- 0 = Ignores the IMB internal FREEZE signal.

- 1 = Finish any current conversion, then freeze

- SUPV Supervisor/Unrestricted Data Space

- 0 = Only the module configuration register, test register, and interrupt register are designated as supervisor-only data space. Access to all other locations is unrestricted.

- 1 = All QADC registers and tables are designated as supervisor-only data space.

IARB[3:0] — Interrupt Arbitration Number

IARB determines QADC interrupt arbitration priority. An IARB field can be assigned a value from %0001 (lowest priority) to %1111 (highest value). Refer to **SECTION 8 IN-TERRUPTS** for more information.

# 3.4 QADC Test Register

# **QADCTEST** — QADC Test Register

\$####02

QADCTEST is used only during factory testing of the MCU.

# 3.5 General-Purpose I/O Port Operation

Each of the port pins, when used as a general-purpose input, is conditioned by a synchronizer with an enable feature. The synchronizer is not enabled until the QADC decodes an IMB bus cycle which addresses the port data register to minimize the high-current effect of mid-level signals on the inputs used for analog signals. Digital input signals must meet the input low voltage ( $V_{IL}$ ) or input high voltage ( $V_{IH}$ ) specifications in **APPENDIX A ELECTRICAL CHARACTERISTICS**. If an analog input pin does not meet the digital input pin specifications when a digital port read operation occurs, an indeterminate state is read.

During a port data register read, the actual value of the pin is reported when its corresponding bit in the data direction register defines the pin to be an input (port A only). When the data direction bit specifies the pin to be an output, the content of the port data register is read. By reading the latch which drives the output pin, software instructions that read data, modify it, and write the result, like bit manipulation instructions, work correctly. When a reduced number of digital port pins are implemented on a particular microcontroller version, the unused bit positions are read as a zero and write operations do not have any effect.

There are two special cases to consider for the digital I/O port operation. When the MUX (externally multiplexed) bit is set in QACR0, the data direction register settings are ignored for the bits corresponding to PQA[2:0], the three multiplexed address (MA[2:0]) output pins. The MA[2:0] pins are forced to be digital outputs, regardless of the data direction setting, and the multiplexed address outputs are driven. The data returned during a port data register read is the value of the multiplexed address latches which drive MA[2:0], regardless of the data direction setting.

Similarly, when an external trigger queue operating mode is selected, the data direction setting for the corresponding pins, PQA3 or PQA4, is ignored. The port pins are forced to be digital inputs for ETRIG1 and/or ETRIG2. The data driven during a port data register read is the actual value of the pin, regardless of the data direction setting.

# 3.5.1 Port Data Register

QADC ports A and B are accessed through two 8-bit port data registers (PORTQA and PORTQB).

Port A pins are referred to as PQA[7:0] when used as a bidirectional 8-bit input/output port that may be used for general-purpose digital input signals or digital open drain pull-down output signals. Port A can also be used for analog inputs (AN[59:52], external trigger inputs (ETRIG[2:1]), and external multiplexer address outputs (MA[2:0]).

Port B pins are referred to as PQB[7:0] when used as an input-only 8-bit digital port that may be used for general-purpose digital input signals. Data for PQB[7:0] is accessed in the lower half of the QPDR. Port B can also be used for nonmultiplexed (AN[51:48]/AN[3:0]) and multiplexed (ANz, ANy, ANx, ANw) analog inputs.

PORTQA and PORTQB are unaffected by reset.

|      | TQA -<br>TQB - |          |         |        | -    |      |      |      |      |      |      |      |      | \$###<br>\$### |      |

|------|----------------|----------|---------|--------|------|------|------|------|------|------|------|------|------|----------------|------|

| 15   | 14             | 13       | 12      | 11     | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1              | 0    |

| PQA7 | PQA6           | PQA5     | PQA4    | PQA3   | PQA2 | PQA1 | PQA0 | PQB7 | PQB6 | PQB5 | PQB4 | PQB3 | PQB2 | PQB1           | PQB0 |

| RE   | SET:           |          |         |        |      |      |      |      |      |      |      |      |      |                |      |

| U    | U              | U        | U       | U      | U    | U    | U    | U    | U    | U    | U    | U    | U    | U              | U    |

| ANA  | LOG CHAN       | INEL:    |         |        |      |      |      |      |      |      |      |      |      |                |      |

| AN59 | AN58           | AN57     | AN56    | AN55   | AN54 | AN53 | AN52 | AN51 | AN50 | AN49 | AN48 | AN3  | AN2  | AN1            | AN0  |

| EXT  | ERNAL TR       | GGER IN  | PUTS:   |        |      |      |      |      |      |      |      |      |      |                |      |

|      |                |          | ETRIG2  | ETRIG1 |      |      |      |      |      |      |      |      |      |                |      |

| MU   | JLTIPLEXE      | D ADDRE  | SS OUTP | UTS:   |      |      |      |      |      |      |      |      |      |                |      |

|      |                |          |         |        | MA2  | MA1  | MA0  |      |      |      |      |      |      |                |      |

| MULT | IPLEXED A      | NALOG IN | VPUTS:  |        |      |      |      |      |      |      |      |      |      |                |      |

|      |                |          |         |        |      |      |      |      |      |      |      | ANz  | ANy  | ANx            | ANw  |

## 3.5.2 Port Data Direction Register

The port data direction register (DDRQA) is associated with the port A digital I/O pins. The bidirectional pins have somewhat higher leakage and capacitance specifications. Refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** for more information. Any bit in this register set to one configures the corresponding pin as an output. Any bit in this register cleared to zero configures the corresponding pin as an input. The software is responsible for ensuring that DDR bits are not set to one on pins used for analog inputs. When the DDR bit is set to one and the pin is selected for analog conversion, the voltage sampled is that of the output digital driver as influenced by the load.

#### NOTE

Caution should be exercised when mixing digital and analog inputs. This should be isolated as much as possible. Rise and fall times should be as large as possible to minimize AC coupling effects.

Since port B is input-only, a data direction register is not needed. Therefore, the lower byte of the port data direction register is not implemented. Read operations on the reserved bits return zeros, and writes have no effect.

| DDRO   | QA —  | Port  | Data  | Direct | tion R | egiste | er    |   |   |   |      |      |   | \$### | #08 |

|--------|-------|-------|-------|--------|--------|--------|-------|---|---|---|------|------|---|-------|-----|

| 15     | 14    | 13    | 12    | 11     | 10     | 9      | 8     | 7 | 6 | 5 | 4    | 3    | 2 | 1     | 0   |

| DDQA7  | DDQA6 | DDQA5 | DDQA4 | DDQA3  | DDQA2  | DDQA1  | DDQA0 |   |   |   | RESE | RVED |   |       |     |

| RESET: |       |       |       |        |        |        |       |   |   |   |      |      |   |       |     |

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

# **SECTION 4 EXTERNAL MULTIPLEXING**

External multiplexer chips concentrate a number of analog signals onto a few inputs to the analog converter. This is helpful in applications that need to convert more analog signals than the A/D converter can normally provide. External multiplexing also puts the multiplex chip closer to the signal source. This minimizes the number of analog signals that need to be shielded due to the close proximity to noisy high speed digital signals at the microcontroller chip.

For example, four 8-input multiplexer chips can be put at the connector where the analog signals first arrive on the computer board. As a result, only four analog signals need to be shielded from noise as they approach the microcontroller chip, rather than having to protect 32 analog signals. However, external multiplexer chips may introduce additional noise and errors if not properly utilized. Therefore, it is necessary to maintain low "on" resistance (the impedance of an analog switch when active within a multiplex chip) and insert a low pass filter (R/C) on the input side of the multiplex chip.

# 4.1 External Multiplexing Operation

The QADC can use from one to four external multiplexer chips to expand the number of analog signals that may be converted. Up to 32 analog channels can be converted through external multiplexer selection. The externally multiplexed channels are automatically selected from the channel field of the conversion command word (CCW) table, the same as internally multiplexed channels. Refer to paragraph 7.7 in **SECTION 7 DIGITAL CONTROL** for additional information on channel number assignments.

All of the automatic queue features are available for externally and internally multiplexed channels. The software selects the external multiplexed mode by setting the MUX bit in control register 0 (QACR0).

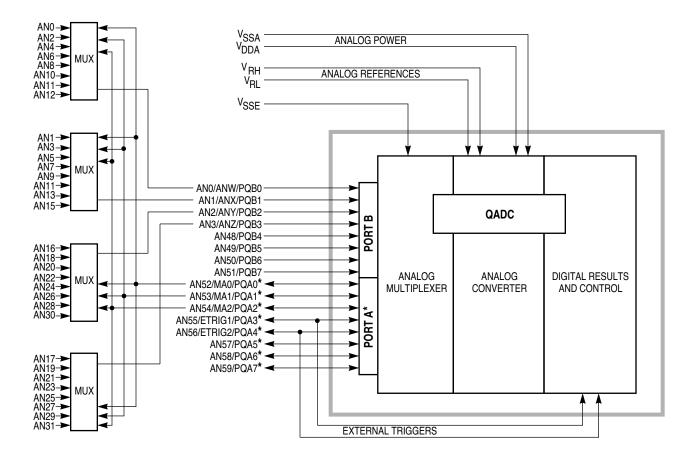

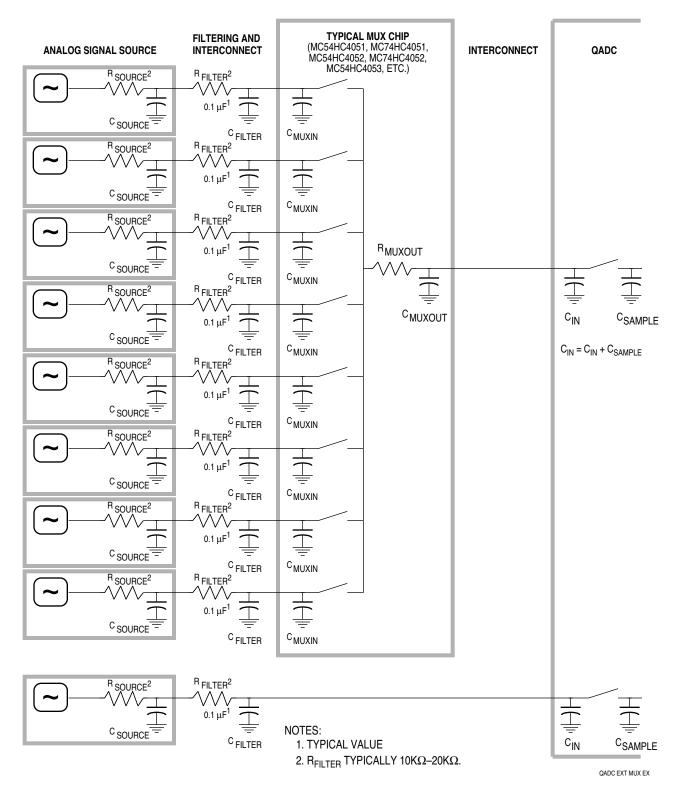

**Figure 4-1** shows the maximum configuration of four external multiplexer chips connected to the QADC. The external multiplexer chips select one of eight analog inputs and connect it to one analog output, which becomes an input to the QADC. The QADC provides three multiplexed address signals — MA0, MA1, and MA2, to select one of eight inputs. These inputs are connected to all four external multiplexer chips. The analog output of the four multiplex chips are each connected to four separate QADC inputs — AN<sub>w</sub>, AN<sub>x</sub>, AN<sub>y</sub>, and AN<sub>z</sub>.

\* PORT A PINS INCORPORATE OPEN DRAIN PULL DOWN DRIVERS.

QADC EXT MUX CONN

## Figure 4-1 Example of External Multiplexing

When the external multiplexed mode is selected, the QADC automatically creates the MA open drain output signals from the channel number in each CCW. The QADC also converts the proper input channel ( $AN_w$ ,  $AN_x$ ,  $AN_y$ , and  $AN_z$ ) by interpreting the CCW channel number. As a result, up to 32 externally multiplexed channels appear to the conversion queues as directly connected signals. The software simply puts the channel number of externally multiplexed channels into CCWs. Refer to **Table 7-9** in **SEC-TION 7 DIGITAL CONTROL** which shows the channel numbers for the externally multiplexed channels that are assigned the range of channel 0 to channel 31.

**Figure 4-1** shows that the three MA signals may also be analog input pins. When external multiplexing is selected, none of the MA pins can be used for analog or digital inputs. They become multiplexed address outputs.

#### 4.2 Module Version Options

The number of available analog channels varies, depending on whether or not external multiplexing is used. A maximum of 16 analog channels are supported by the internal multiplexing circuitry of the converter. **Table 4-1** shows the total number of analog input channels supported with zero to four external multiplexer chips. The QADC uses 21 pins which allow a maximum of 41 analog channels to be converted.

| Number of Analog Input Channels Available<br>Directly Connected + External Multiplexed = Total Channels <sup>1, 2</sup> |                          |                           |                             |                            |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------|-----------------------------|----------------------------|--|--|--|--|--|--|--|

| No External<br>Mux Chips                                                                                                | One External<br>Mux Chip | Two External<br>Mux Chips | Three External<br>Mux Chips | Four External<br>Mux Chips |  |  |  |  |  |  |  |

| 16                                                                                                                      | 12 + 8 = 20              | 11 + 16 = 27              | 10 + 24 = 34                | 9 + 32 = 41                |  |  |  |  |  |  |  |

NOTES:

1. The above assumes that the external trigger inputs are shared with two analog input pins.

When external multiplexing is used, three input channels become multiplexed address outputs, and for each external multiplexer chip, one input channel becomes a multiplexed analog input.

# **SECTION 5 PIN CONNECTION CONSIDERATIONS**

The QADC requires accurate, noise-free input signals for proper operation. This section discusses the design of external circuitry to maximize QADC performance.

# 5.1 Analog Reference Pins

No A/D converter can be more accurate than its analog reference. Any noise in the reference can result in at least that much error in a conversion. The reference for the QADC, supplied by pins  $V_{RH}$  and  $V_{RL}$ , should be low-pass filtered from its source to obtain a noise-free, clean signal. In many cases, simple capacitive bypassing may suffice. In extreme cases, inductors or ferrite beads may be necessary if noise or RF energy is present. Series resistance is not advisable since there is an effective DC current requirement from the reference voltage by the internal resistor string in the RC DAC array. External resistance may introduce error in this architecture under certain conditions. Any series devices in the filter network should contain a minimum amount of DC resistance.

For accurate conversion results, the analog reference voltages must be within the limits defined by  $V_{DDA}$  and  $V_{SSA}$ , as explained in the following subsection.

## 5.2 Analog Power Pins

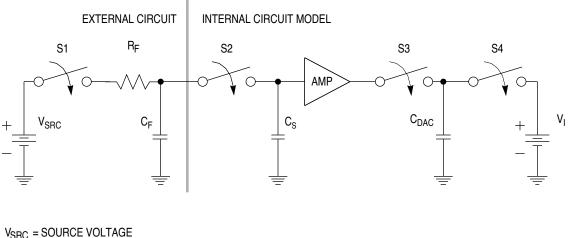

The analog supply pins ( $V_{DDA}$  and  $V_{SSA}$ ) define the limits of the analog reference voltages ( $V_{RH}$  and  $V_{RL}$ ) and of the analog multiplexer inputs. **Figure 5-1** is a diagram of the analog input circuitry.

Figure 5-1 Analog Input Circuitry

Since the sample amplifier is powered by  $V_{DDA}$  and  $V_{SSA}$ , it can accurately transfer input signal levels up to but not exceeding  $V_{DDA}$  and down to but not below  $V_{SSA}$ . If the input signal is outside of this range, the output from the sample amplifier is clipped.

In addition, V<sub>RH</sub> and V<sub>RL</sub> must be within the range defined by V<sub>DDA</sub> and V<sub>SSA</sub>. As long as V<sub>RH</sub> is less than or equal to V<sub>DDA</sub> and V<sub>RL</sub> is greater than or equal to V<sub>SSA</sub> and the sample amplifier has accurately transferred the input signal, resolution is ratiometric within the limits defined by V<sub>RL</sub> and V<sub>RH</sub>. If V<sub>RH</sub> is greater than V<sub>DDA</sub>, the sample amplifier can never transfer a full-scale value. If V<sub>RL</sub> is less than V<sub>SSA</sub>, the sample amplifier can never transfer a zero value.

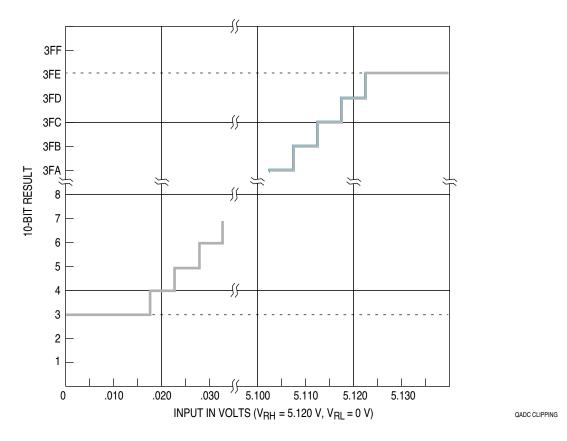

**Figure 5-2** shows the results of reference voltages outside the range defined by  $V_{DDA}$  and  $V_{SSA}$ . At the top of the input signal range,  $V_{DDA}$  is 10 mV lower than  $V_{RH}$ . This results in a maximum obtainable 10-bit conversion value of 3FE. At the bottom of the signal range,  $V_{SSA}$  is 15 mV higher than  $V_{RL}$ , resulting in a minimum obtainable 10-bit conversion value of three.

Figure 5-2 Errors Resulting from Clipping

# 5.3 Analog Supply Filtering and Grounding

Two important factors influencing performance in analog integrated circuits are supply filtering and grounding. Generally, digital circuits use bypass capacitors on every  $V_{DD}/V_{SS}$  pin pair. This applies to analog subsystems or submodules also. Equally important as bypassing is the distribution of power and ground.

Analog supplies should be isolated from digital supplies as much as possible. This necessity stems from the higher performance requirements often associated with analog circuits. Therefore, deriving an analog supply from a local digital supply is not recommended. However, if for economic reasons digital and analog power are derived from a common regulator, filtering of the analog power is recommended in addition to the bypassing of the supplies already mentioned. For example, an RC low pass filter could be used to isolate the digital and analog supplies when generated by a common regulator. If multiple high precision analog circuits are locally employed (i.e. two A/D converters), the analog supplies should be isolated from each other as sharing supplies introduces the potential for interference between analog circuits.

Grounding is the most important factor influencing analog circuit performance in mixed signal systems (or in standalone analog systems). Close attention must be paid not to introduce additional sources of noise into the analog circuitry. Common sources of noise include ground loops, inductive coupling, and combining digital and analog grounds together inappropriately.

The problem of how and when to combine digital and analog grounds arises from the large transients which the digital ground must handle. If the digital ground is not able to handle the large transients, the current from the large transients can return to ground through the analog ground. It is the excess current overflowing into the analog ground which causes performance degradation by developing a differential voltage between the true analog ground and the microcontroller's ground pin. The end result is that the ground observed by the analog circuit is no longer true ground and often ends in skewed results.

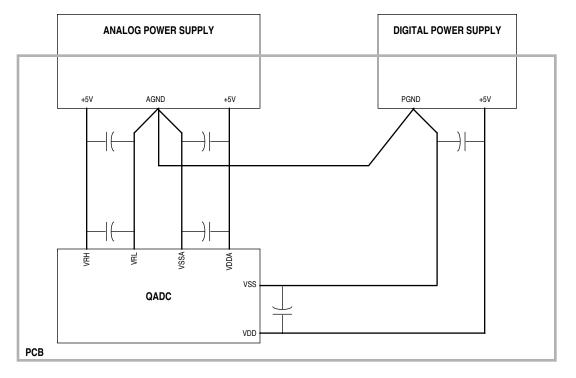

Two similar approaches designed to improve or eliminate the problems associated with grounding excess transient currents involve star-point ground systems. One approach is to star-point the different grounds at the power supply origin, thus keeping the ground isolated. Refer to **Figure 5-3**.

QADC POWER SCHEM

# Figure 5-3 Star-Ground at the Point of Power Supply Origin

Another approach is to star-point the different grounds near the analog ground pin on the microcontroller by using small traces for connecting the non-analog grounds to the analog ground. The small traces are meant only to accommodate DC differences, not AC transients.

#### NOTE

This star-point scheme still requires adequate grounding for digital and analog subsystems in addition to the star-point ground. Other suggestions for PCB layout in which the QADC is employed include:

- Analog ground must be low impedance to all analog ground points in the circuit.

- Bypass capacitors should be as close to the power pins as possible.

- The analog ground should be isolated from the digital ground. This can be done by cutting a separate ground plane for the analog ground.

- Non-minimum traces should be utilized for connecting bypass capacitors and filters to their corresponding ground/power points.

- Minimum distance for trace runs when possible.

## 5.4 Accommodating Positive/Negative Stress Conditions

Positive or negative stress refers to conditions which exceed nominally defined operating limits. Examples include applying a voltage exceeding the normal limit on an input (for example, voltages outside of the suggested supply/reference ranges) or causing currents into or out of the pin which exceed normal limits. QADC specific considerations are voltages greater than  $V_{DDA}$ ,  $V_{RH}$  or less than  $V_{SSA}$  applied to an analog input which cause excessive currents into or out of the input. Refer to **APPENDIX A ELECTRICAL CHARACTERISTICS** for more information on exact magnitudes.

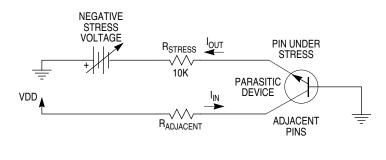

Both stress conditions can potentially disrupt conversion results on neighboring inputs. Parasitic devices, associated with CMOS processes, can cause an immediate disruptive influence on neighboring pins. Common examples of parasitic devices are diodes to substrate and bipolar devices with the base terminal tied to substrate ( $V_{SSI}/V_{SSA}$  ground). Under stress conditions, current introduced on an adjacent pin can cause errors on adjacent channels by developing a voltage drop across the adjacent external channel source impedances.

**Figure 5-4** shows an active parasitic bipolar when an input pin is subjected to negative stress conditions. Positive stress conditions do not activate a similar parasitic device.

QADC PAR STRESS CONN

# Figure 5-4 Input Pin Subjected to Negative Stress

The current out of the pin  $(I_{OUT})$  under negative stress is determined by the following equation:

$$I_{OUT} = \frac{\left|V_{STRESS} - V_{BE}\right|}{R_{STRESS}}$$

where:

V<sub>STRESS</sub> = Adjustable voltage source

$V_{BE}$  = Parasitic bipolar base/emitter voltage (refer to  $V_{NEGCLAMP}$  in **AP-PENDIX A ELECTRICAL CHARACTERISTICS**)

R<sub>STRESS</sub> = Source impedance (10K resistor in **Figure 5-4** on stressed channel)

The current into  $(I_{IN})$  the neighboring pin is determined by the 1/K<sub>N</sub> (Gain) of the parasitic bipolar transistor (1/K<sub>N</sub><sup>((1)</sup>).

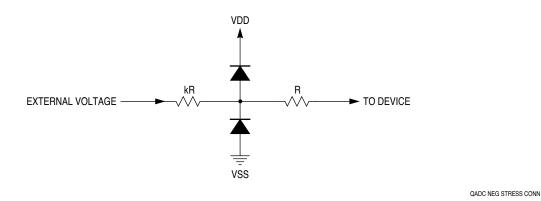

One way to minimize the impact of stress conditions on the QADC is to apply voltage limiting circuits such as diodes to supply and ground. However, leakage from such circuits and the potential influence on the sampled voltage to be converted must be considered. Refer to **Figure 5-5**.

Figure 5-5 Voltage Limiting Diodes in a Negative Stress Circuit

Another method for minimizing the impact of stress conditions on the QADC is to strategically allocate QADC inputs so that the lower accuracy inputs are adjacent to the inputs most likely to see stress conditions.

Finally, suitable source impedances should be selected to meet design goals and minimize the effect of stress conditions.

# 5.5 Analog Input Considerations

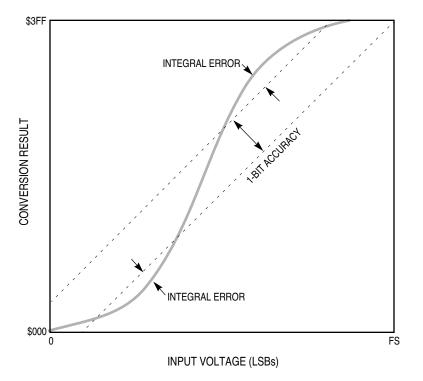

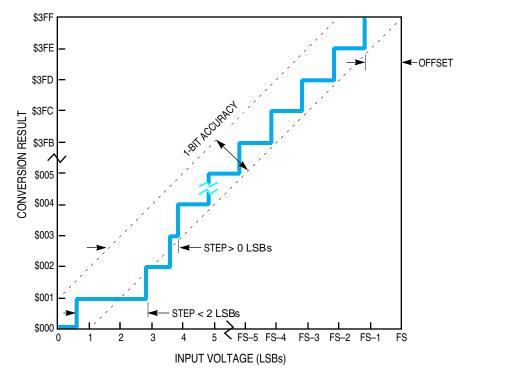

The source impedance of the analog signal to be measured and any intermediate filtering should be considered whether external multiplexing is used or not. **Figure 5-6** shows the connection of eight typical analog signal sources to one QADC analog input pin through a separate multiplexer chip. Also, an example of an analog signal source connected directly to a QADC analog input channel is displayed.