SynDEx-Ic est un logiciel d'aide au prototypage rapide d'applications

temps réel qui permet la synthèse automatique de circuits ASIC

et de circuits reconfigurables de type FPGA. C'est un logiciel libre

développé à l'ESIEE par l'équipe "Conception d'architecture"

du laboratoire A2SI, c'est une extension du logiciel SynDEx

de l'INRIA.

Les architectures matérielles supportées actuellement par

SynDEx sont des architectures de type "multiprocesseurs hétérogènes"

(architectures basées sur des composants programmables à jeux

d'instruction figé de type microprocesseurs, microcontrôleur, DSP,

station de travail, utilisation d'ASIC dédiés). En générant

du VHDL synthétisable, SynDEx-Ic, quand à lui, permet de

couvrir les architectures basées sur des circuits dédiés

de type ASIC et/ou FPGA.

SynDEx implémente la méthodologie Adéquation Algorithme

Architecture développée à l'INRIA. Les travaux issus

de deux thèses en collaboration avec l'INRIA (Ailton

Dias, Linda Kaouane)

ont permis d'étendre cette méthodologie aux architectures à

base de circuits (reconfigurables ou non) : l'algorithme à implanter

est spécifié sous la forme d'un graphe flot de données

conditionné factorisé hiérarchique saisi à l'aide

de l'interface graphique du logiciel. L'objectif est de trouver hors-ligne (i.e.

avant l'exécution) une implantation de l'algorithme qui respecte une

contrainte de latence donnée (durée d'exécution) tout en

étant implantable sur le circuit ciblé (en terme de ressources

utilisées, par exemple le nombre de CLB pour un FPGA). Pour cela

nous avons choisi de travailler sur la factorisation, c'est à dire dérouler

plus ou moins les boucles : plus une boucle est déroulée, plus

il y a de parallélisme, plus il est possible de diminuer la latence,

mais en contrepartie la surface nécessaire à son implantation

augmente. Il s'agit donc d'explorer les boucles et boucles imbriquées

de façon à trouver pour chaque boucle le taux de défactorisation

(taux de déroulage) qui permet de respecter les contraintes d'exécution

données. Comme il est impossible d'explorer toutes les possibilités

de défactorisation dans des temps raisonnables, il faut utiliser des

méthodes approchées basées sur des heuristiques. Nous avons

développé plusieurs heuristiques capable de rechercher des taux

de déroulage de boucles permettant de faire tenir l'application dans

le circuit (contrainte de surface) tout en respectant la contrainte de latence

spécifiée. Il s'agit d'heuristiques gloutones couplées

avec des heuristiques de recuit simulé. Le résultat de l'heuristique

est ensuite transformé en un code VHDL directement synthétisable

pour être exécuté sur le composant cible ou bien pour être

simulé.

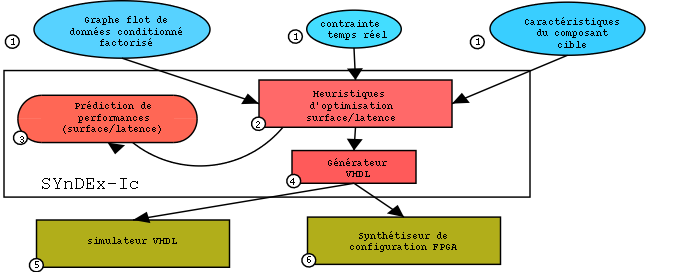

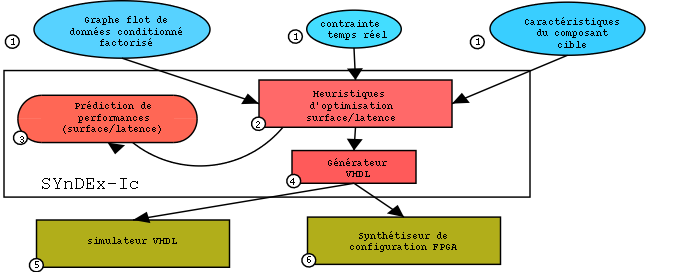

Le schéma ci-dessous illustre les différentes étapes du processus de prototypage avec SynDEx-Ic :