Voici un exemple de spécification d'un filtre adaptatif fournit avec SynDEx dans le fichier "ega.sdx". Nous allons utiliser SynDEx-Ic pour générer le code VHDL de cette application.

Comme tous les algorithmes spécifié dans SynDEx; cet algorithme est réactif : il est répété infiniment en boucle (on parlera d'itération infinie), pour chaque donnée (ou ensemble de données) d'entrée est calculée une valeur (ou ensemble de valeurs) de sortie.

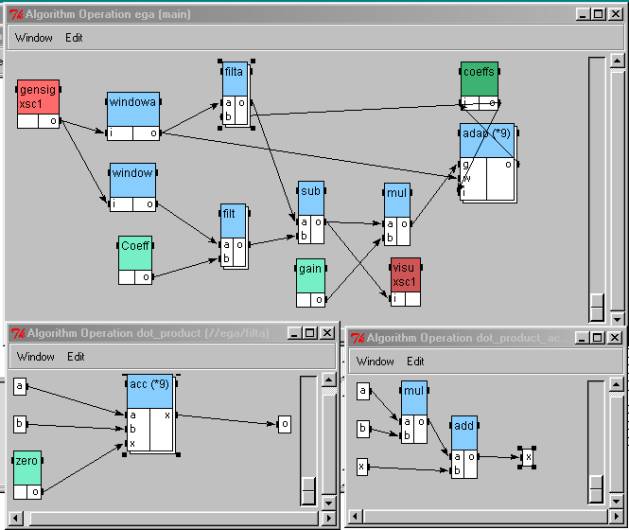

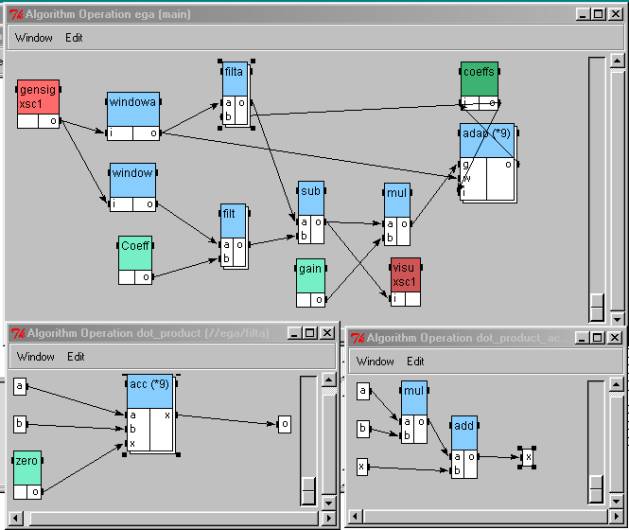

Sur la figure suivante, la fenêtre du haut représente l'algorithme complet : chaque boite représente une opération de calcul sans effet de bord (bleue), une opération d'entrée-sortie (rouge), une mémorisation (vert foncé) qui sert à transmettre certaine données d'une itération sur l'autre, et enfin les constantes (vert clair).

La fenêtre en bas à gauche de cette même figure représente l'intérieur de la boîte "filta" de la partie du haut. Filta est composée de 9 fois l'exécution de "acc" lui même décrit par la partie de la figure en bas à droite : un produit-accumulation. Ce facteur 9 indique que les données d'entrées a et b de filta (resp. acc) sont des vecteurs de 9 éléments. Le produit-accumulation se fera sur les 9 composantes de ces vecteurs. On fait donc la somme des produits des composantes des vecteurs d'entrées a et b (en effet, dans "acc" décrit par le graphe en bas à droite, le résultat de la somme (boite "add") est copié dans la sortie x qui est aussi une entrée de acc).

A partir de ce graphe d'algorithme d'entrée, SynDEx-Ic construit le graphe de voisinage ce qui correspond à la synthèse du chemin de contrôle (boîte rose sur le schéma si-dessous) :

La figure suivante est un exemple de graphe de voisinage construit à partir de l'exemple d'algorithme donné en haut de cette page : chaque boite rectangulaire correspond à l'unité de contrôle d'une frontières de répétition : les arcs verts pointent sur les opérations contrôlés par la frontière (il lui appartiennent), alors que les arcs rouges, noirs et bleus montrent les relations de dépendances (inclusion, mise en séquence, concurrence) des unités de contrôle.

Nos heuristiques explorent l'espace de solutions afin de trouver le compromis surface (nombre de CLB, opérateur FF, FG), temps (latence) qui repecte la contrainte de latence donnée (ceci est une capture d'écran de SynDEx-Ic V6.0, l'heuristique n'est pas encore disponible dans la version mise en ligne)

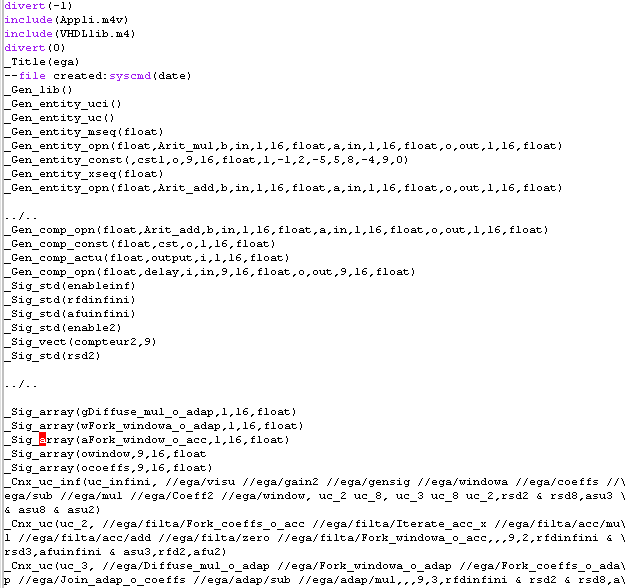

A partir du graphe flot de données spécifié ainsi que des choix de défactorisation effectués par l'heuristique, SynDEx-Ic génère un macro code intermédiaire (compatible avec le macro processeur m4), cette étape intermédiaire permet d'avoir un générateur de code indépendant du langage final (verilog etc). En voici un extrait (vous pouvez télécharger les fichiers en 2 parties ici et là, ou bien le générer vous même avec SynDEx-Ic) :

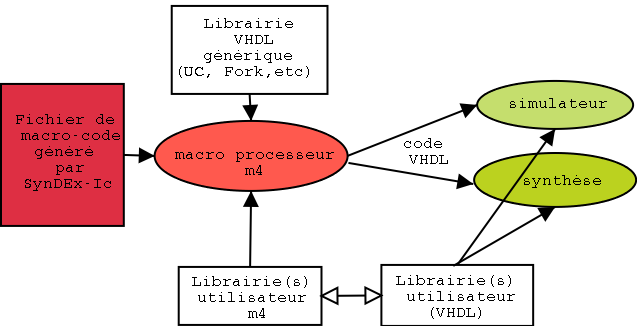

Ce macro code est ensuite automatiquement transformé en un code VHDL structurel à l'aide du macro processeur gnu-m4 et de bibliothèques de définition. A chaque opération du graphe d'algorithme qui ne se définit pas par un sous-graphe doit correspondre un composant VHDL dans l'une des bibliothèques :

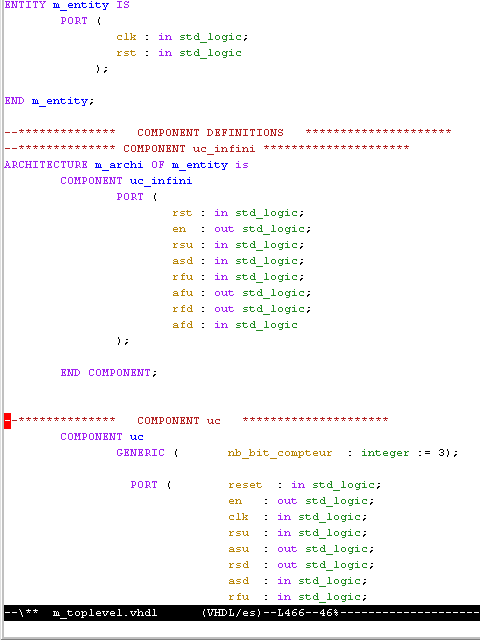

Voici un extrait du code VHDL obtenu, téléchargeable intégralement en 2 parties : ici et là (ou que vous pouvez générer vous même avec SynDEx-Ic)

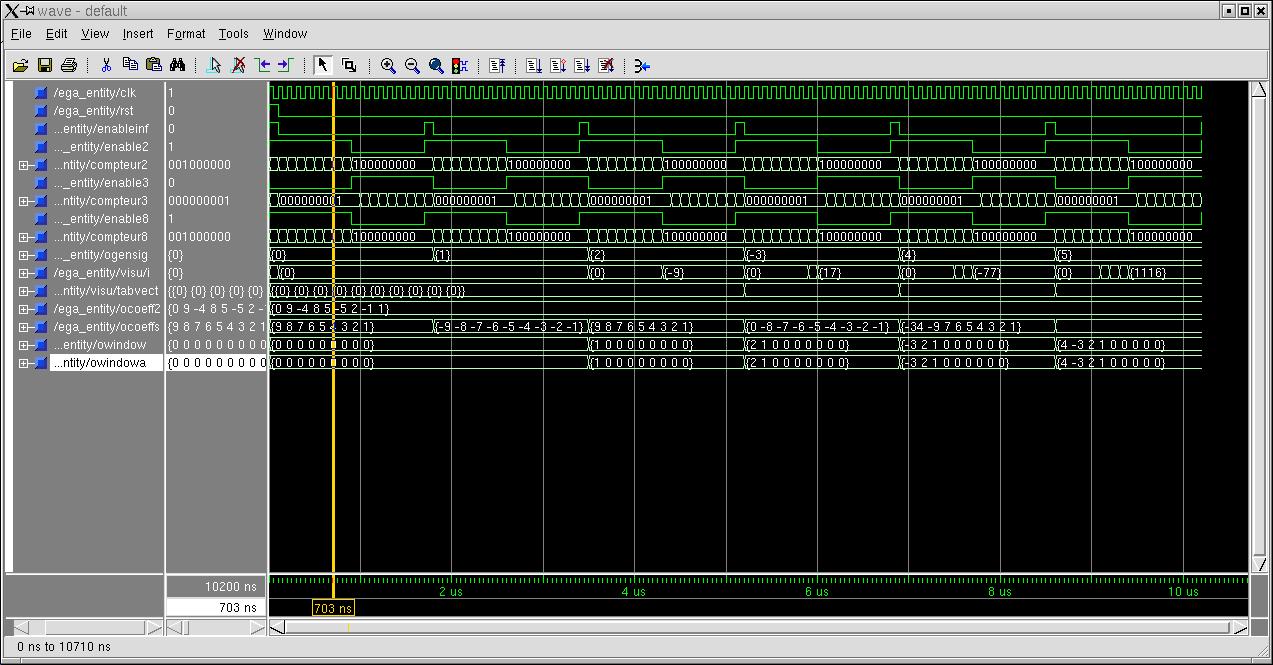

Vous pouvez ensuite envoyer ce code dans un simulateur (ici Modelsim); voici une copie d'écran :

Dernière mise à jour : 15 Avril 2008 par Thierry Grandpierre.